### **Application note**

Authors: Kali Naraharisetti Peter B. Green

### About this document

#### Scope and purpose

The purpose of this document is to provide a comprehensive functional description of and guide to using the DEMO\_200W\_12VDC two-stage PFC + LLC resonant converter evaluation board based on the following ICs: IR1155S, IRS27952, IRS11688 and ICE5QR0680AG. The following document describes its operation and covers technical aspects essential to the design process, including calculation of external component values, MOSFET selection and PCB layout optimization, as well as additional protection circuitry. Test results and waveforms are also included.

#### **Intended** audience

Power supply design engineers, applications engineers, students.

### **Table of contents**

| Abou  | t this document                                              | 1   |

|-------|--------------------------------------------------------------|-----|

| Table | e of contents                                                | 1   |

| 1     | Introduction                                                 | 3   |

| 2     | Evaluation board specifications                              | 5   |

| 3     | Schematics                                                   | 6   |

| 4     | PFC section                                                  | .10 |

| 4.1   | PFC modes of operation                                       | 11  |

| 5     | IR1155S functional overview                                  | .13 |

| 5.1   | Key features of the IR1155S                                  | .14 |

| 6     | PFC boost stage dimensioning                                 | .18 |

| 7     | IR1155S control circuit design                               | .21 |

| 7.1   | CS resistor (ISNS pin)                                       | 21  |

| 8     | IRS27952 functional overview                                 | .24 |

| 9     | LLC resonant half-bridge converter operation                 | .25 |

| 9.1   | Important points to consider when designing an LLC converter | .28 |

| 9.2   | First Harmonic Approximation (FHA)                           | 29  |

| 9.3   | Dead-time calculations                                       | .40 |

| 9.4   | OVP circuit (hiccup mode operation)                          | .45 |

| 9.5   | Over-current protection                                      | .46 |

| 9.6   | Short-circuit protection                                     | .47 |

| 10    | IRS11688 functional overview                                 | .48 |

# infineon

## Design of 200 W boost PFC plus HB LLC resonant converter with IR1155, IRS27952 and IR11688

### Introduction

| 10.1  | MOT resistor calculation                              |    |

|-------|-------------------------------------------------------|----|

| 11    | ICE5QR0680AG functional overview                      | 53 |

| 11.1  | Quasi-Resonant (QR) flyback converter operation       | 53 |

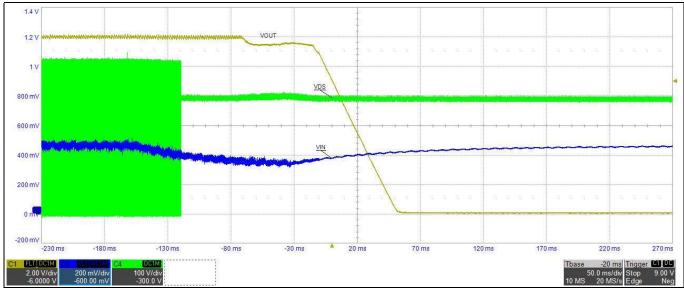

| 11.2  | Brown-out protection                                  | 57 |

| 12    | Bill of Materials (BOM)                               | 58 |

| 13    | PCB layout                                            | 63 |

| 13.1  | PCB layout guidelines for system optimization         | 65 |

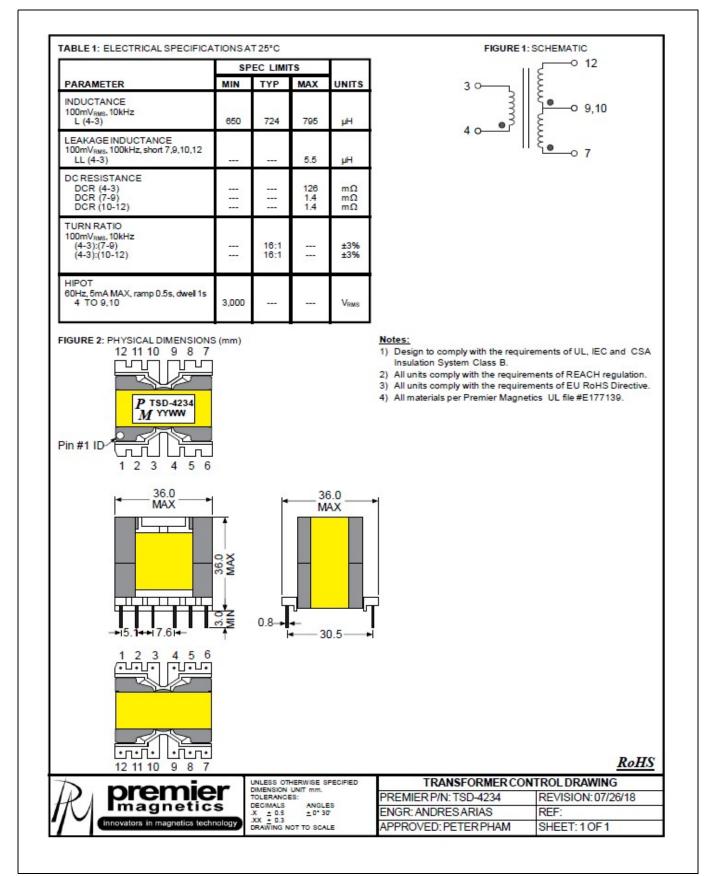

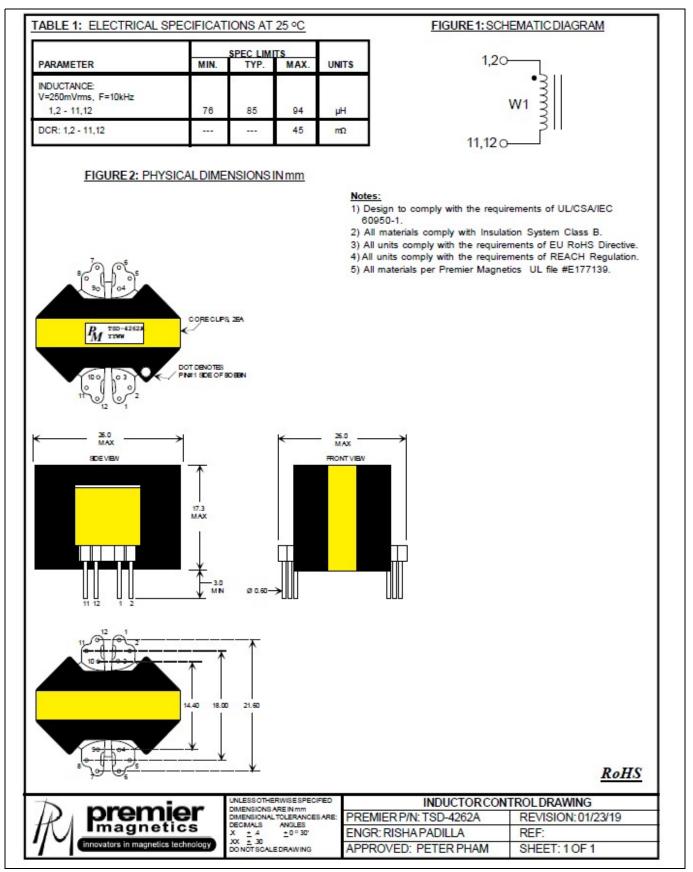

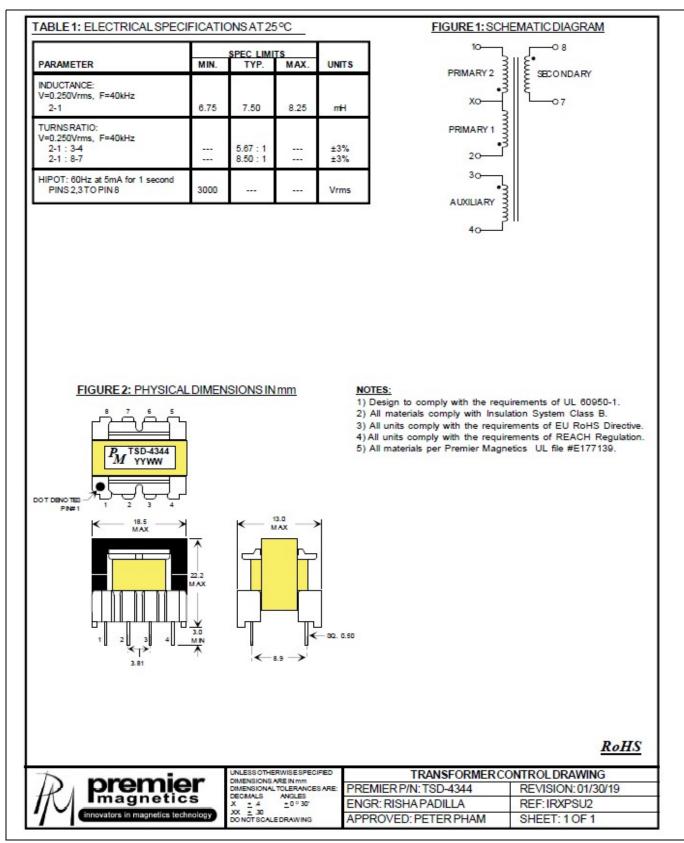

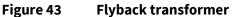

| 14    | Transformer and inductor specifications               | 67 |

| 14.1  | PCB inductor                                          | 67 |

| 14.1  | LLC transformer                                       | 68 |

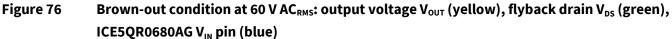

| 14.2  | Resonant inductor                                     | 69 |

| 14.3  | Flyback transformer (coupled inductor)                | 70 |

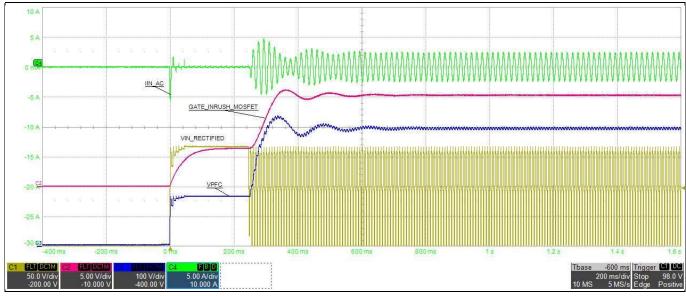

| 15    | Test results                                          | 71 |

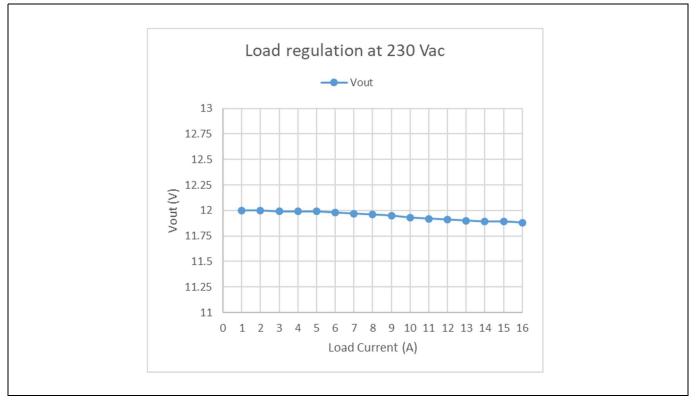

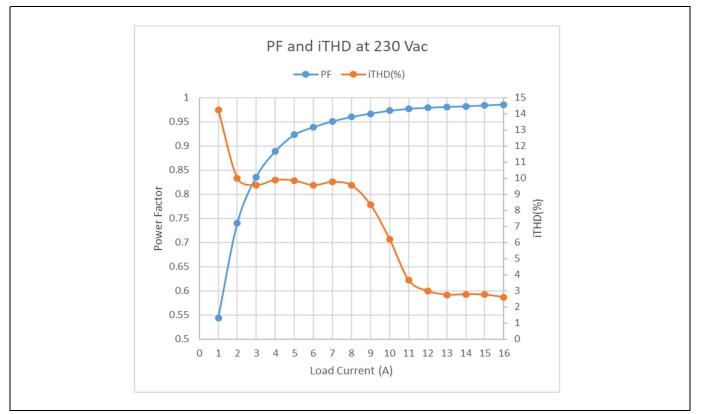

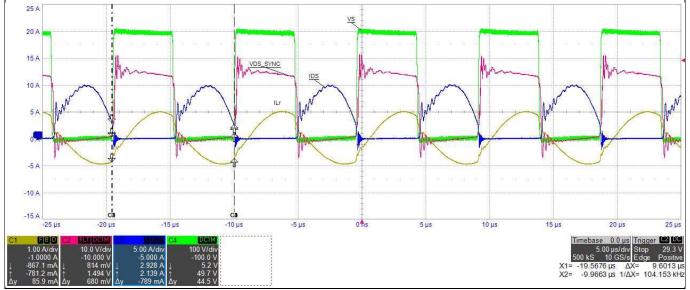

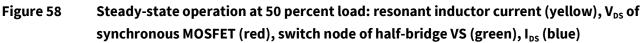

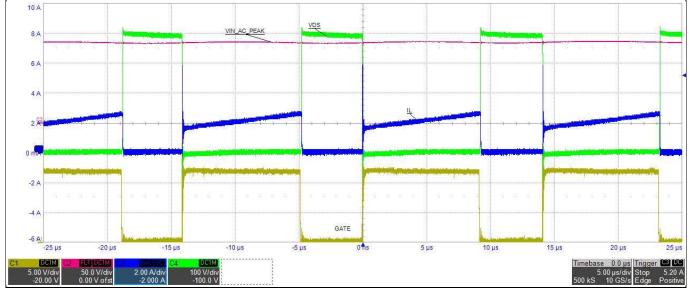

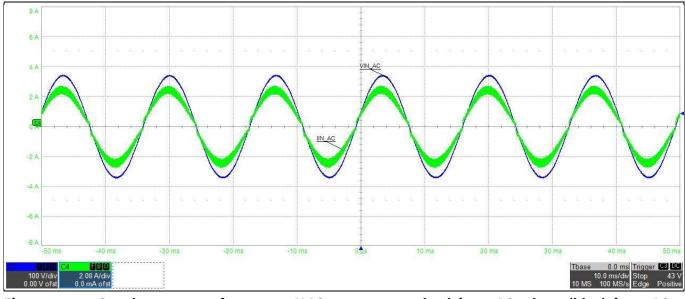

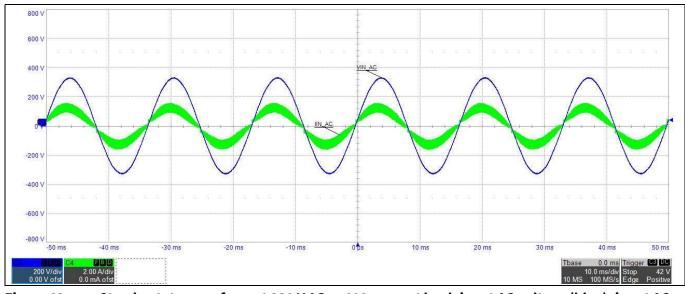

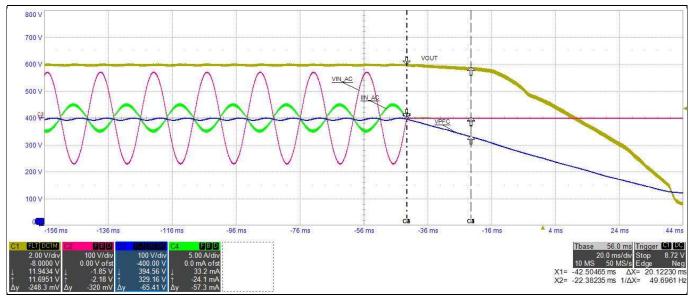

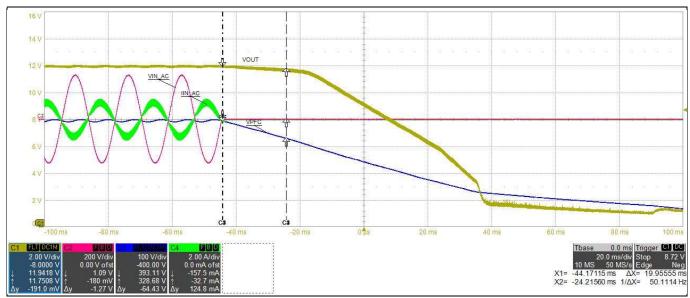

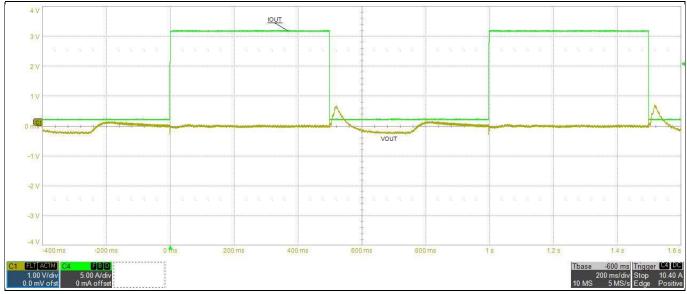

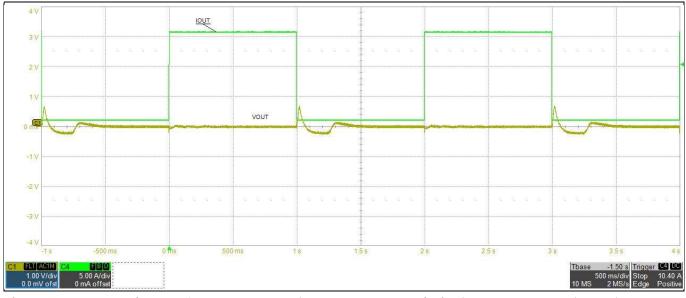

| 15.1  | Operation under different line and load conditions    | 71 |

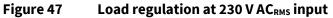

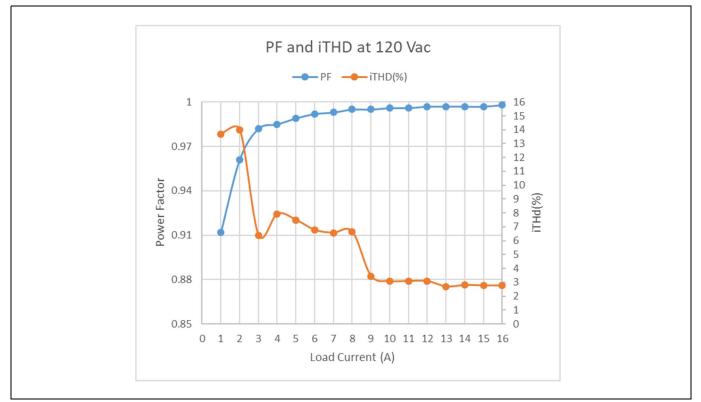

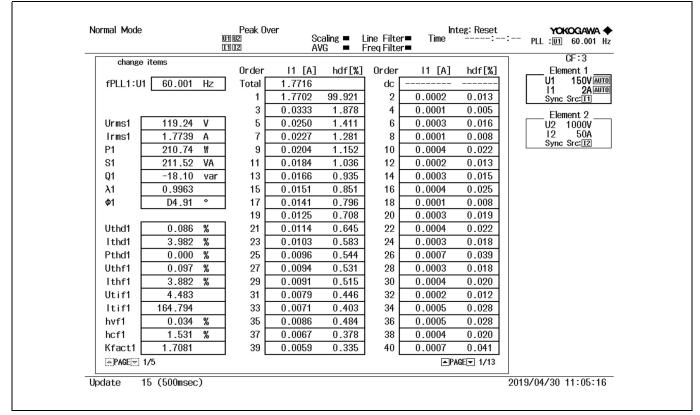

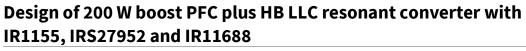

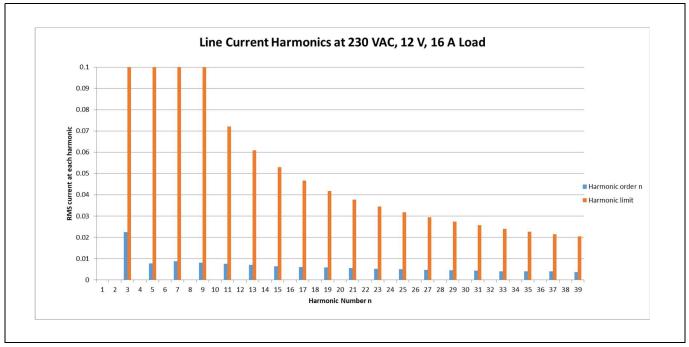

| 15.2  | Power factor and input current harmonics (iTHD)       | 74 |

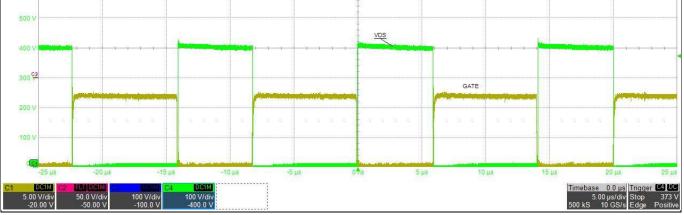

| 15.1  | Operating waveforms                                   | 78 |

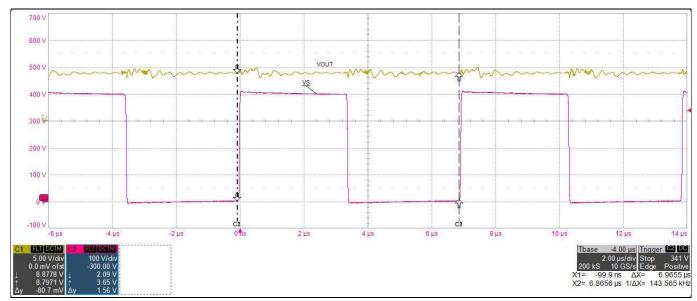

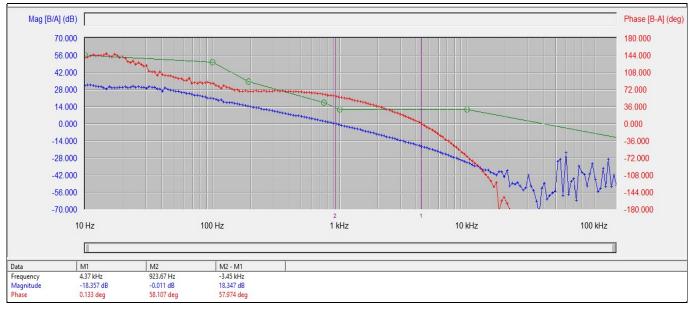

| 15.2  | Closed-loop frequency response                        | 90 |

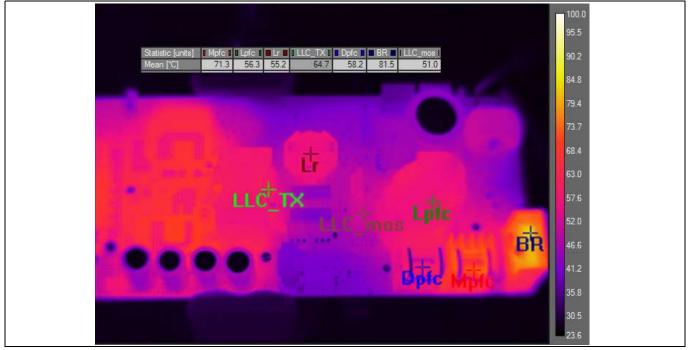

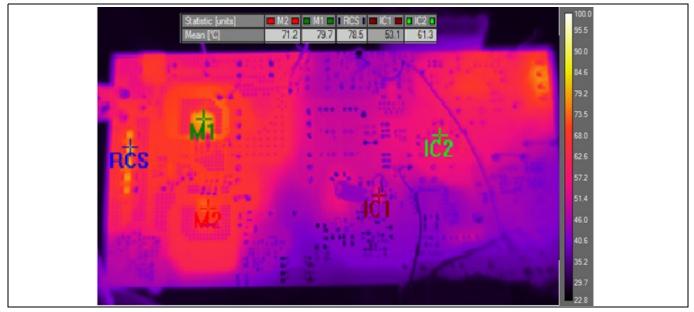

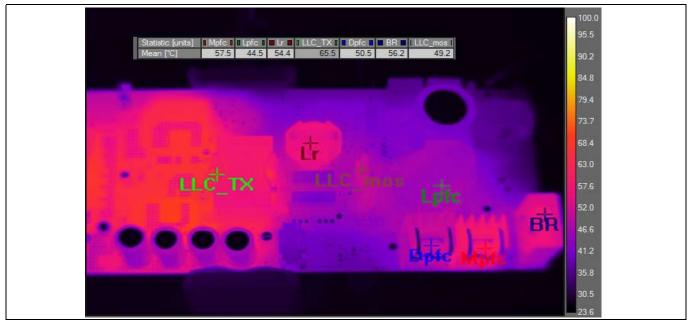

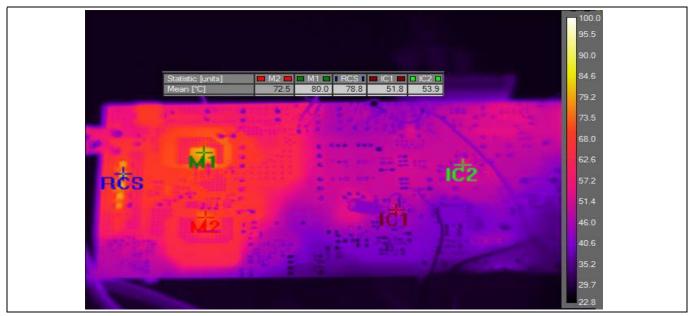

| 15.3  | Thermal performance under normal operating conditions | 91 |

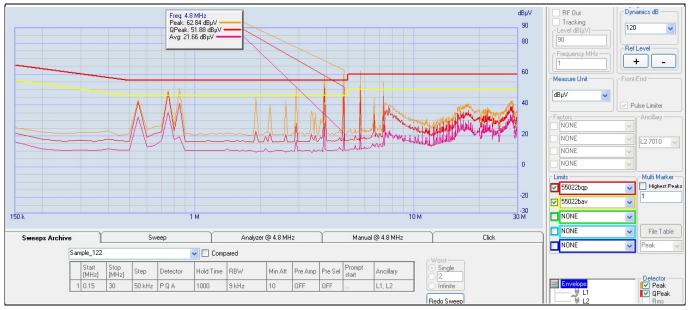

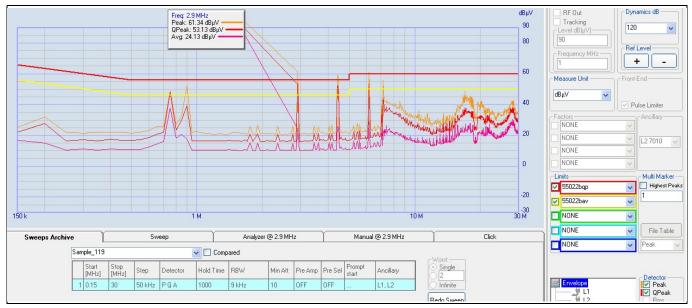

| 15.4  | Conducted EMI                                         | 93 |

| 16    | Conclusion                                            | 95 |

| Refer | rences                                                | 96 |

| Revis | sion history                                          | 97 |

## 1 Introduction

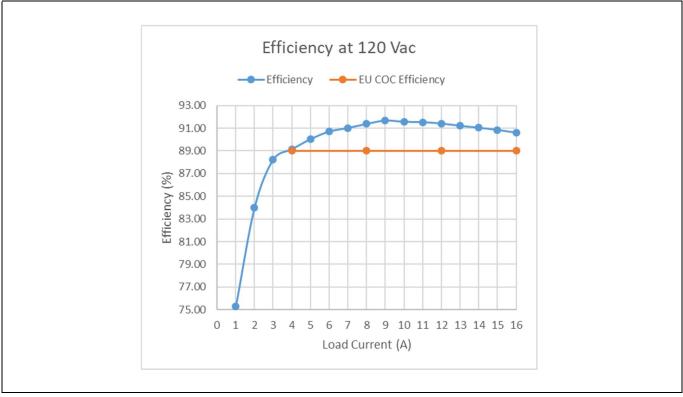

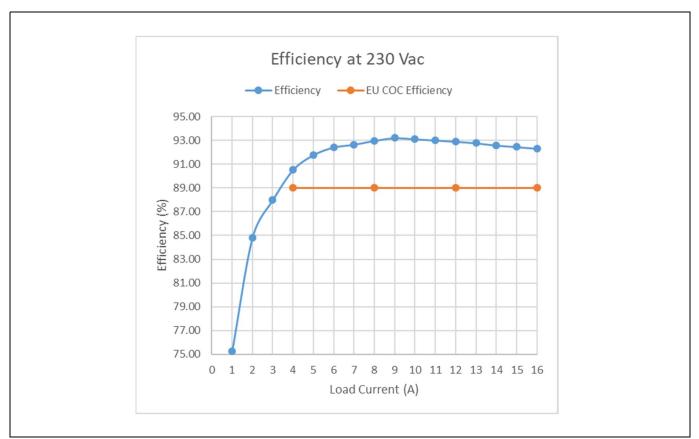

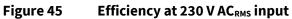

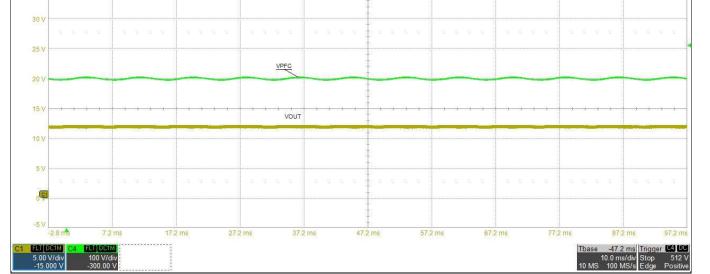

The DEMO\_200W\_12VDC\_LLC evaluation board is an off-line isolated power supply designed to provide a 12 V DC output up to amaximum load of 16 A operating from a 50/60 Hz AC-line input voltage between 85 and 265 V AC. The output of this evaluation board is protected against over-load and short-circuit. An over-voltage protection circuit is also included to limit the output voltage. At light loads. This application note gives a detailed description of a 192 W (12 V/16 A) two-stage isolated constant voltage regulated PFC boost plus resonant LLC half-bridge SMPS evaluation board with synchronous rectification based on the IR1155, IRS27952 and IR11688 controllers. Detailed test results and operating waveforms are provided. The board meets an average efficiency of at least 89 percent to meet the European Code of Conduct (EU COC) and US Department of Energy (US DOE) standards for 25 percent, 50 percent, 75 percent and 100 percent loads.

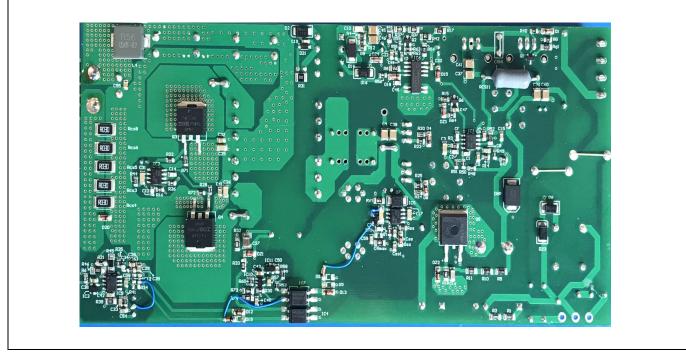

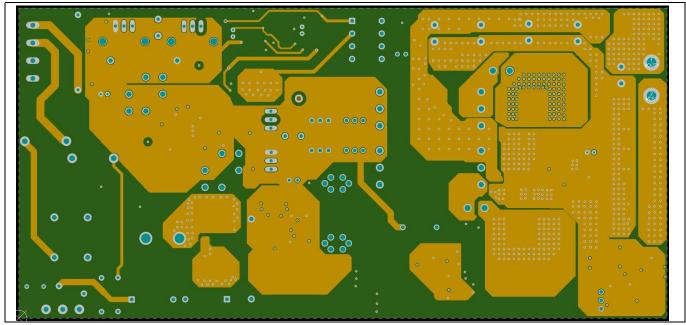

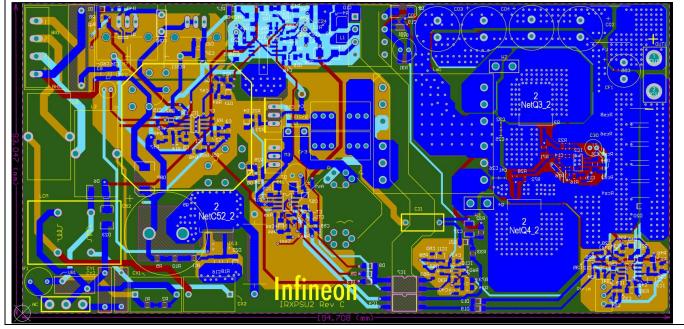

Figure 1 DEMO\_200W\_12VDC\_LLC two-stage PFC boost + LLC resonant converter demo board (top view)

Introduction

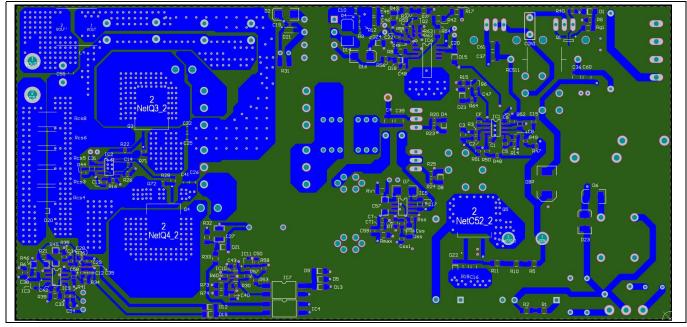

Figure 2 DEMO\_200W\_12VDC\_LLC two-stage PFC boost + LLC resonant converter demo board (bottom view)

**Evaluation board specifications**

## 2 Evaluation board specifications

#### Input and output at normal operation

- AC input voltage 85 to  $265 V_{RMS}$  (55 to 65 Hz)

- Output voltage 12 V

- Output current 16 A

- Maximum output continuous power 192 W

- PF greater than 0.9 at maximum load, 85 V AC to 265 V AC input voltage

- Total Harmonic Distortion (iTHD) less than 20 percent at maximum load, to 265 V<sub>RMS</sub> input voltage

- Average four-point efficiency greater than 89 percent at 120 and 230 V<sub>RMS</sub> input voltage

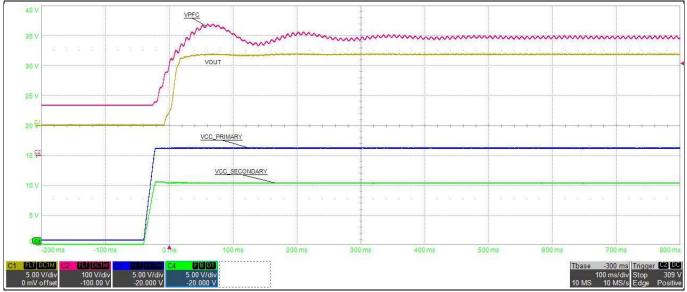

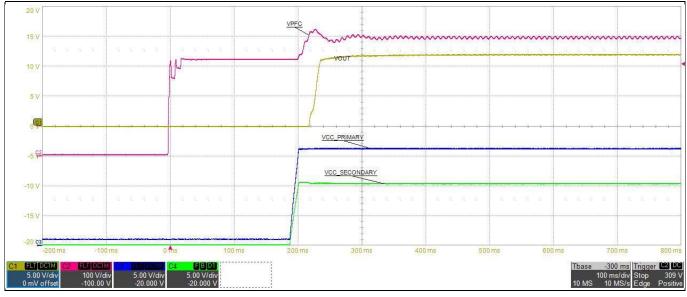

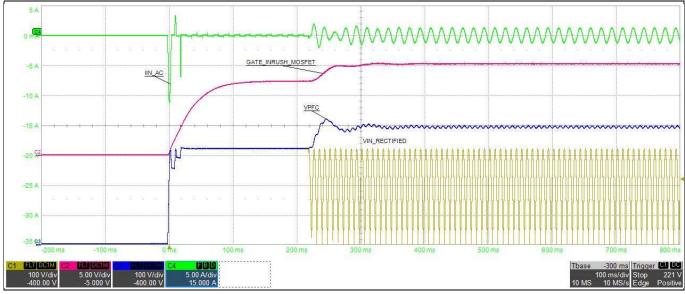

- Start-up time to reach the secondary nominal output voltage during full-load condition at 120 and 230 V<sub>RMS</sub> input voltage less than 300 ms

#### **Protection features**

- Output Over-Voltage Protection (OVP) at  $V_{OUT}$  less than or equal to 16 V

- Over-Current Protection (OCP) at 19 A, hiccup mode

- Short-Circuit Protection (SCP), hiccup mode

- Brown-out protection, shut-down at 60 to 65 V<sub>RMS</sub>, start-up at 75 to 80 V<sub>RMS</sub> AC input voltages

#### **No-load operation**

- Burst mode during no-load condition

- Maximum power loss during no-load condition is 1 W at 120 and 230 V<sub>RMS</sub> input voltage

#### Maximum component temperature

In an ambient temperature of 30°C, the maximum allowed component temperatures are as follows:

- Resistors less than 100°C

- Ceramic capacitors, film capacitors and electrolytic capacitors less than 100°C

- PFC, Flyback, LLC transformers less than 100°C

- MOSFET transistors and diodes less than 100°C

- ICs less than 100°C

#### Dimensions of evaluation board

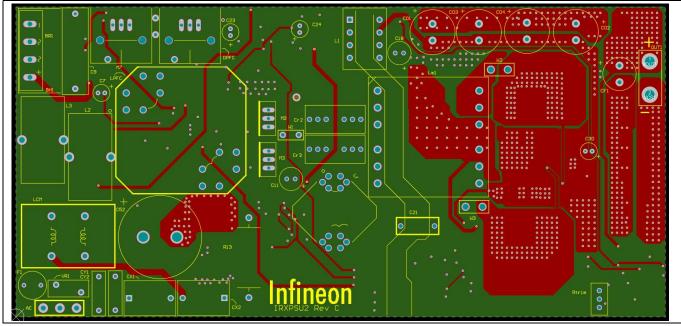

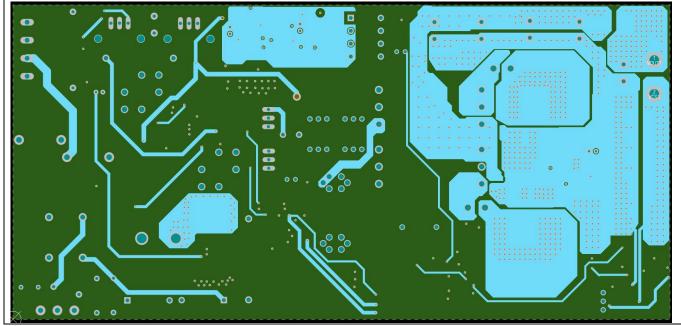

Maximum width 7.66 inches (194.7 mm), maximum length 3.66 inches (93.04 mm).

#### WARNING!

The board should be tested only by qualified engineers and technicians.

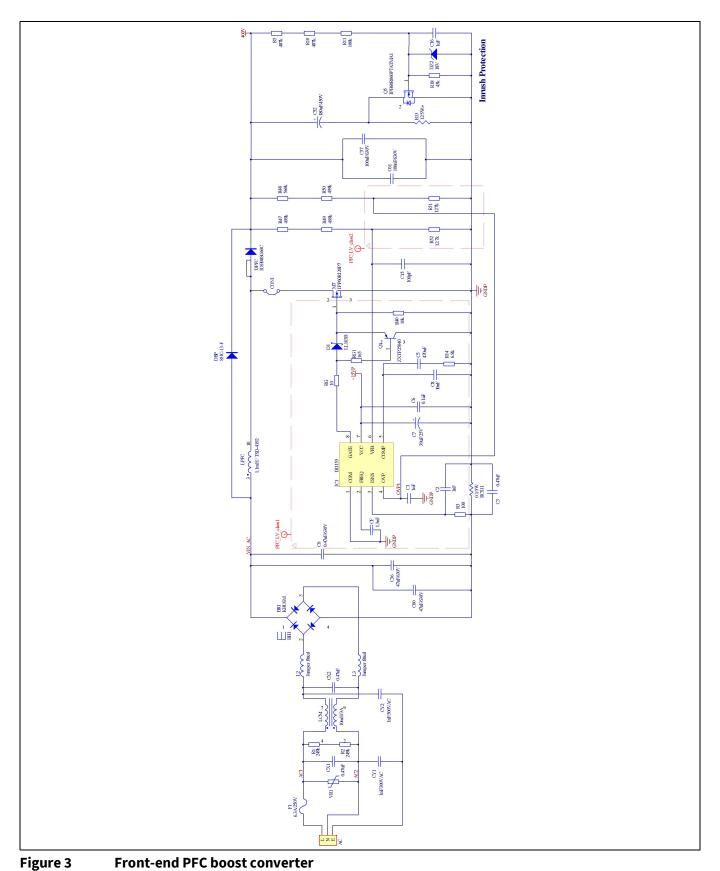

3 Schematics

V 2.2

## Design of 200 W boost PFC plus HB LLC resonant converter with IR1155, IRS27952 and IR11688

**PFC** section

### 4 PFC section

DEMO\_200W\_12VDC\_LLC is a two-stage topology power converter demo board based on a PFC boost preregulator followed by a half-bridge LLC resonant converter. It provides a constant voltage output of 12 V over a wide AC-line voltage input range with high power factor and low total harmonic distortion of the line input current (iTHD). The evaluation board has a 12 V DC output up to 16 A and AC-line input voltage range between 85 and 265 V AC 50/60 Hz.

Many electronic appliances incorporate Switch Mode Power Supplies (SMPS), which traditionally include capacitive line filtering circuitry followed by a bridge rectifier and bulk capacitor to provide a DC bus voltage to supply a DC-DC converter. Without PFC circuitry such an SMPS draws a high peak current at the voltage peak and almost no current over the remainder of the cycle, resulting in a typical power factor of around 0.5 containing high THD. Low power factor leads to the circulation of RMS current greater than that necessary to perform the required work. This excess current flows in the conductors, forcing utility companies to oversize their distribution networks. In some countries the utility companies charge their end users in the event that the annual amount of reactive power exceeds a certain value [4]. PFC circuitry is often added to enable the appliance to draw an almost sinusoidal current from the AC-line with negligible phase shift that has very low harmonic distortion. This provides the best possible load for the power transmission grid so that power may be supplied without additional conduction losses in transmission lines or burden on transformers and generators.

Power factor consists of two distinct components - distortion and phase displacement [4].

- 1) Displacement factor ( $k_{\phi}$ ): This is the phase difference between input voltage and current (V AC and  $I_{AC}$ ), which is defined as cosine phi (cos  $\phi$ ).

- 2) *Distortion factor* (k<sub>d</sub>): This parameter quantifies the degree of distortion of the AC input current. A sinusoidal signal is composed purely of fundamental frequency with no harmonic content.

Power Factor (PF) =

$$\frac{I_{1,rms}}{I_{rms}} \text{Cos} \phi = k_d \cdot k_{\phi}$$

Where  $k_{\emptyset} = \cos \phi$  is called the displacement factor where  $\phi$  represents the displacement angle between voltage and current fundamentals, and  $k_d = \frac{I_{1,rms}}{I_{rms}}$  is called the distortion factor.  $I_{1,rms}$  is the RMS amplitude of the fundamental and  $I_{rms}$  is the total RMS value of the complete current signal. THD of the current is often referred to as iTHD to differentiate it from the voltage THD. The line voltage should remain sinusoidal.<sup>1</sup>

PFC shapes the input current of the power supply, causing it to be in synchronization with the mains voltage. In an ideal PFC circuit the input current follows the input voltage as in a purely resistive load with no input current harmonics [6]. Although active PFC may be achieved with several topologies, the boost converter (Figure 7) is the most popular solution for the following reasons:

- The input current of the boost converter is continuous, as opposed to the discontinuous input current of the buck, buck-boost or flyback topologies. The continuous input current is much easier to filter, which is a major advantage of this topology because any additional filtering needed at the converter input would increase cost and reduce the power factor due to capacitive loading of the line. A discontinuous input current waveform would also increase EMI, requiring further filtering.

- A buck converter is not suitable, because when the input voltage falls below the output voltage, no power can be transferred, creating a drop-out period depending on the output voltage, which inevitably results in low power factor and high iTHD.

<sup>&</sup>lt;sup>1</sup> Power factor and iTHD measurements should be carried out using a pure sinewave AC source, otherwise voltage distortion would produce inaccurate results.

**PFC** section

- The buck-boost converter produces an output which is negative and not preferred. The input current is not continuous, and additionally the MOSFET has high voltage stress  $(V_{in} + V_o)$ .

- The flyback converter is able provide isolation, though this is usually done in the DC-DC stage and is therefore unnecessary in the PFC stage. It also has a discontinuous input current and requires more components and larger magnetics, leading to a higher Bill of Materials (BOM) cost. The front-end stage in this demo board is a PFC boost converter topology, which operates in Continuous Conduction Mode (CCM) using average current mode control.

## 4.1 PFC modes of operation

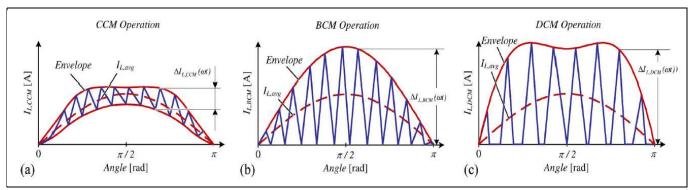

The different operating modes are briefly described as follows: Continuous Conduction Mode (CCM), Discontinuous Conduction Mode (DCM) and Critical Conduction Mode (CrCM).<sup>1</sup> Figure 8 illustrates the boost inductor current waveforms and the average input current in the three operating modes. DCM operation may appear to be simpler than CrCM, since it can operate at constant switching frequency; however, it has a higher peak input current than CrCM, which in turn has a higher peak than CCM. DCM is therefore less efficient and also requires the most filtering.

Figure 7 Boost inductor current for different operating modes: (a) CCM, (b) CrCM, (c) DCM [7]

In CrCM, the inductor current is forced to operate at the boundary between CCM and DCM. CrCM generally uses constant on-time control in which the switching frequency changes during the AC-line cycle. Each new switching cycle begins when the energy stored in the inductor has been fully transferred to the output, therefore the off-time varies during the AC-line cycle, becoming longer at the peak [8]. The reset time for the inductor varies, causing the frequency to adjust in order to maintain the boundary mode operation. CrCM requires the controller to sense the inductor current zero crossing in order to trigger the start of the next switching cycle. The inductor current ripple (or the peak current) in CrCM is twice the average value, which increases the MOSFET RMS currents and turn-off current. However, since every switching cycle starts at zero current and usually with ZVS operation, turn-on loss of the MOSFET is eliminated. Also, since the output diode turns off at zero current, reverse recovery losses and EMI are eliminated as well. On balance the high input ripple current and its impact on the input EMI filter tends to eliminate the benefit of CrCM mode for higher-power designs unless interleaved stages are used to reduce the input HF current ripple, which can enable a highly efficient design but at substantially higher cost [6]. The main differences between CCM and CrCM relate to the current ripple profile and switching frequency, which affect RMS current, switching power losses and the filter design.

CCM operation requires a higher inductor value compared to CrCM; however, the core loss and the winding loss are lower due to the lower peak and RMS currents. In the case of CCM PFC, the inductor current ripple is typically designed to be 20 to 40 percent of the average input current.

<sup>&</sup>lt;sup>1</sup> Critical conduction mode is sometimes referred to in the literature as "boundary" mode (BCM or BM) or "transition" mode (TM). Application Note 11 of 98

This has several advantages:

- Peak current is lower and the RMS current factor with a trapezoidal waveform is reduced compared to a triangular waveform, thereby reducing conduction losses.

- Turn-off losses are lower due to switch-off at lower peak current.

- The HF ripple current, which needs to be smoothed by the input EMI filter, is much lower in amplitude.

On the other hand, CCM encounters the turn-on losses in the MOSFET, which can be exacerbated by the output diode reverse recovery loss due to reverse recovery charge Qrr. For this reason ultra-fast recovery silicon diodes or silicon carbide Schottky diodes with extremely low Qrr are necessary for CCM mode. In conclusion, for low-power applications the CrCM boost PFC converter has the advantage of power saving and improving power density up to 100 to 150 W. Above this range CCM starts to become a better option for medium- to high-power applications.

IR1155S functional overview

## 5 IR1155S functional overview

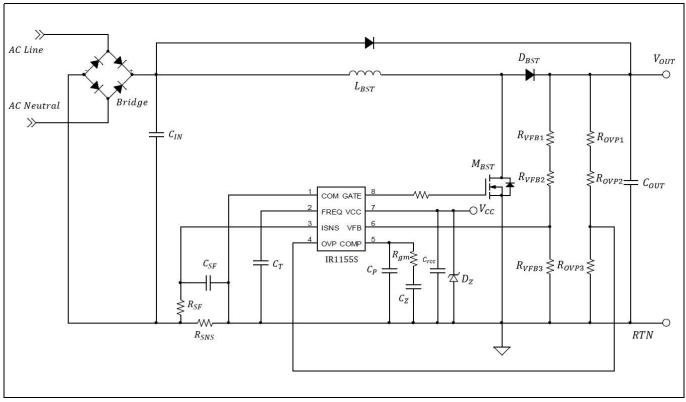

The  $\mu$ PFC IR1155S PFC IC is based on Infineon's proprietary One Cycle Control (OCC) technique, which provides high power factor, low THD and an excellent DC bus regulation while enabling reduction of component count, PCB area and design time when compared to traditional solutions. The IR1155S is a fixed-frequency PFC IC designed to operate in CCM with average current mode control. It incorporates programmable switching frequency, programmable soft-start, micro-power start-up current, and user-initiated micro-power sleep mode for compliance with standby energy standards with ultra-low bias currents for sensing pins. The switching frequency can be set from 48 kHz to 200 kHz. In addition it includes dedicated OVP, cycle-by-cycle peak current limit, Open-Loop Protection (OLP) and V<sub>cc</sub> Under Voltage Lock-Out (UVLO).

Figure 8 IR1155-based PFC boost converter

The diagram above shows the system application diagram of the IR1155S-based PFC converter. There are three input pins – VFB, COMP and ISNS – which provide the necessary signals to achieve PFC and maintain output voltage regulation. The functions of the above-mentioned inputs are as follows:

- VFB provides DC output bus voltage feedback sensing for voltage regulation

- COMP used for compensating the voltage feedback loop to set the correct transient response characteristics

- ISNS provides sensing of the inductor current, which is used to determine the PFC switching duty cycle

Essentially, there are two control loops in the control algorithm: a slow outer voltage loop whose function is to maintain output voltage regulation, and a fast inner current loop whose function is to determine the instantaneous duty cycle for each switching cycle. The current-shaping function, i.e. PFC, is achieved primarily by the current loop. The voltage loop is responsible only for controlling the magnitude of the input current in order to maintain DC bus voltage regulation.

**IR1155S functional overview**

|            | Pin | Name | Description                       |

|------------|-----|------|-----------------------------------|

| IR1155S    | 1   | СОМ  | Ground                            |

| COM GATE   | 2   | FREQ | Frequency set                     |

| 7          | 3   | ISNS | Current sense                     |

| FREQ VCC   | 4   | OVP  | Output over-voltage detect/enable |

| ISNS VFB 6 | 5   | СОМР | Voltage loop compensation         |

|            | 6   | VFB  | Output voltage sense              |

| OVP COMP   | 7   | VCC  | IC supply voltage                 |

|            | 8   | GATE | Gate drive output                 |

Figure 9 IR1155S pin assignments

### 5.1 Key features of the IR1155S

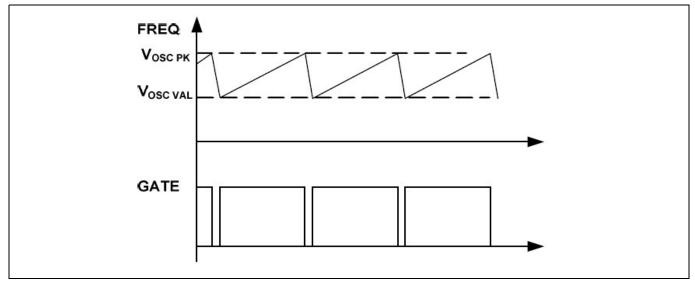

#### 1. Programmable oscillator

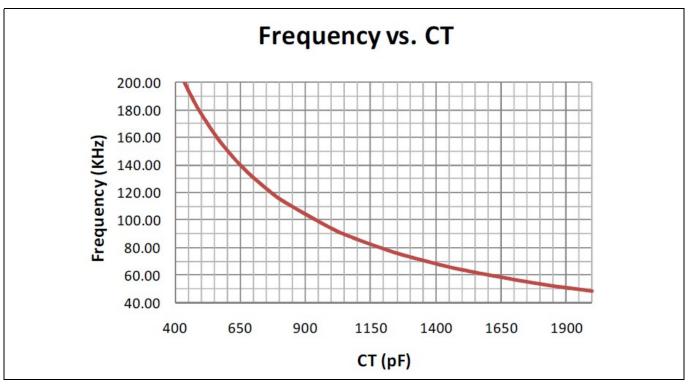

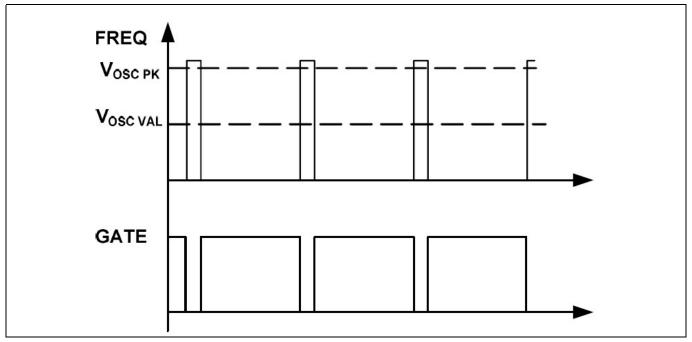

The switching frequency of IR1155S is programmed by a capacitor (CT) connected from the FREQ pin to the IC ground. The switching frequency can be set in the range of 48 to 200 kHz with capacitor values ranging from 430 pF to 2 nF. A 200  $\mu$ A constant current source  $I_{(OSC(CHG))}$  is used to charge the capacitor voltage from  $V_{(OSC(VAL))}$  (2 V typical) to  $V_{(OSC(PK))}$  (4 V typical). Once the voltage at CT reaches the 4 V threshold, the charging current is disconnected and a 6.6 mA discharging current source  $I_{(OSC(CHG))}$  is activated to discharge CT. When the voltage is discharged to 2 V, the discharging current is discontinued and the charging current source will be turned on again. In this way a sawtooth waveform is produced at the FREQ pin, as shown in figure 9. The rising slope of the sawtooth defines the maximum duty cycle of the GATE output, which is shown in figure 10. In the system the actual duty for each switching cycle is determined by the OCC modulator and may vary from minimum 0 percent to maximum 96~99 percent. The relationship between CT and the switching frequency is outlined in figure 11.

#### IR1155S functional overview

Figure 11 IR1155S programmable switching frequency

Using an external capacitor to set the frequency improves the oscillator noise immunity and also provides the option to synchronize the IR1155S to an external clock pulse. In this case, the clock should be a narrow pulse with 1~5 percent duty cycle. The duty cycle of the sync pulse defines the dead-time of the GATE output such that 1 percent sync duty-cycle results in 99 percent maximum PFC GATE output. For this reason, a smaller sync duty cycle is preferred to achieve lower THD. However, it is necessary for the minimum clock pulse to be longer than 100 ns to guarantee reliable operation. The amplitude of the sync signal should be higher than V<sub>OSC(PK)</sub>.

Figure 12 Synchronizing the IR1155S with an external signal

\_\_\_\_\_

#### 2. Programmable soft-start

The IR1155S facilitates programmability of the system soft-start time, allowing the designer freedom to choose the converter start-up time appropriate for the application. The soft-start time is defined as the time required for the V<sub>COMP</sub> voltage to charge through its entire dynamic range, i.e. from 0 V to V<sub>COMP, EFF</sub>. As a result, the soft-start time is dependent on the component values selected for compensation of the voltage loop at the COMP pin, primarily the CZ capacitor. As V<sub>COMP</sub> voltage rises gradually, the IR1155S allows a higher and higher RMS current into the PFC converter. This controlled increase of the input current serves to reduce system component stress during start-up. During soft-start the controller is capable of full duty-cycle modulation (from zero to MAX DUTY), based on the instantaneous I<sub>SNS</sub> signal from system Current Sense (CS) input. Furthermore, the IR1155S internal logic ensures that the soft-start capacitor is discharged when the IC enters sleep or standby mode in order to facilitate soft-start on restart.

#### 3. User-initiated micro-power sleep mode

The IR1155S has an ENABLE function embedded in the OVP/EN pin. When this pin voltage is actively pulled below  $V_{SLEEP}$  threshold, the IC is pushed into sleep mode, where the current consumption is less than 200  $\mu$ A even when  $V_{CC}$  is above the  $V_{CC(ON)}$  threshold. The system designer can use an external logic-level signal to access the ENABLE feature, since the  $V_{SLEEP}$  threshold is so low. The IR1155S internal logic ensures that  $V_{COMP}$  is discharged before the IC enters sleep mode in order to enable soft-start on resumption of operation.

#### 4. Over-Voltage Protection (OVP)

The OVP pin is a dedicated pin for OVP that also safeguards the system if there is a break in the VFB feedback loop due to the resistor divider becoming disconnected. An over-voltage fault is triggered when the OVP pin voltage exceeds the  $V_{OVP}$  threshold of 106.5 percent of  $V_{REF}$ . The IR1155S gate drive is immediately set low. The over-voltage fault is removed and gate drive re-enabled only when both pin voltages are below the  $V_{OVP(RST)}$  threshold of 102.2 percent of  $V_{REF}$ . The OVP level can be programmed through an external resistor divider.

#### 5. *Open-Loop Protection (OLP)*

The OLP ensures that the IC is restrained in standby mode if the VFB pin voltage has not exceeded or has dropped below the  $V_{OLP}$  threshold of 19 percent of  $V_{REF}$ . In standby mode, all internal circuitry of the IC remains biased, the gate drive is disabled and current consumption is in the low milliamp range. During start-up, if for some reason the voltage feedback loop is open, the IR1155S will remain in standby and not start, thus avoiding a potentially catastrophic failure.

#### 6. Cycle-by-cycle peak current limit protection (IPK LIMIT)

The cycle-by-cycle peak current limit is triggered when the V<sub>ISNS</sub> pin voltage exceeds the V<sub>ISNS(PK)</sub> threshold of -0.77 V (in magnitude). When this condition is encountered, the IC gate drive is immediately disabled and held in that state until the I<sub>SNS</sub> pin voltage falls below V<sub>ISNS(PK)</sub>. Even though the IR1155S operates based on average current mode control, the input to the peak current limit comparator is decoupled from the averaging circuit, thus enabling instantaneous cycle-by-cycle protection for peak current limitation.

#### 7. $V_{cc} UVLO$

In the event that the voltage at the V<sub>cc</sub> pin should drop below the V<sub>cc</sub> UVLO turn-off threshold V<sub>cc(UVLO</sub>), the IC enters UVLO mode, the gate drive is terminated and the turn-on threshold V<sub>cc(ON)</sub> must again be exceeded in order to re-start the process. In UVLO mode, the current consumption is less than 175  $\mu$ A.

PFC boost stage dimensioning

## 6 PFC boost stage dimensioning

| Table 1 PFC converter specifi | cations                             |

|-------------------------------|-------------------------------------|

| AC input voltage              | 85 to 264 V <sub>RMS</sub>          |

| Input line frequency          | 47 to 63 Hz                         |

| Nominal DC output voltage     | 400 V                               |

| Maximum output power          | 210 W                               |

| Power factor                  | 0.99 at 120 V <sub>RMS</sub> /210 W |

|                               | 0.99 at 230 V <sub>RMS</sub> /210 W |

| Minimum output hold-up time   | 20 ms                               |

| Maximum soft-start time       | 40 ms                               |

| Switching frequency           | 70 kHz                              |

| Over-voltage protection       | 440 V                               |

|                               |                                     |

#### Table 1 PFC converter specifications

#### 1. Peak input current

It is necessary to determine the maximum input currents (RMS and peak) from the specifications in table 1 before proceeding with detailed design of the PFC boost converter. The maximum input current condition occurs at the highest load and lowest line input voltage (210 W at 85 V AC). Assuming a nominal efficiency of 93 percent, the maximum input power can be determined:

$$P_{IN(MAX)} = \frac{P_{o(MAX)}}{\eta_{MIN}} = \frac{210 \, W}{0.93} = 225.81 \, W$$

<sup>[1]</sup>

From this, the maximum RMS AC-line current is then calculated:

$$I_{IN(RMS) MAX} = \frac{P_{o(MAX)}}{PF.\eta_{MIN}.V_{IN(RMS)MIN}} = \frac{210 W}{0.99.0.93.85 V} = 2.66 A$$

[2]

The selection of the semiconductor components (bridge rectifier, boost switch and boost diode) is based on  $I_{IN(RMS)MAX}$ .

Assuming a pure sinusoidal input, the maximum peak AC-line current can then be calculated:

$$I_{IN(PK) MAX} = \frac{\sqrt{2}P_{IN(MAX)}}{V_{IN(RMS)MIN}} = \frac{\sqrt{2}.225.81 W}{85 V} = 3.76 A$$

[3]

2. Boost inductance

The IR1155S is an average current mode controller. An on-chip RC filter is sized to effectively filter the boost inductor current ripple to generate a clean average current signal for sensing. The averaging function in the IC can accommodate a maximum limit of 40 percent inductor current ripple factor at maximum input current. The inductance has to be sized so that the ripple current factor is not more than 40 percent at maximum input current condition (at the peak of AC sinusoid). This is because:

• Higher ripple current factors would interfere with the average current mode operation of the OCC algorithm in the IR1155S, leading to duty-cycle instabilities and pulse skipping, resulting in current distortion and sometimes even audible noise.

PFC boost stage dimensioning

• Power devices are stressed with higher ripple currents, as the peak inductor current (I<sub>L(PK)MAX</sub>) increases proportionately. In this calculation, an inductor current ripple factor of 25 percent is selected. The ripple current at the peak of the AC sinusoid at maximum input current is:

$$\Delta I_L = 0.25 \cdot I_{IN(PK)MAX} = 0.25 \cdot 3.757A = 0.939A$$

[4]

And, the peak inductor current is:

$$I_{\rm L(PK)\,MAX} = I_{IN(PK)MAX} + \frac{\Delta I_L}{2} = 3.757\,A + \frac{0.939\,A}{2} = 4.227\,A$$

[5]

In order to determine the boost inductance, the power switching duty cycle at the peak of AC sinusoid (at lowest input line of 85 V AC) is required.

$$V_{IN(PK)MIN} = \sqrt{2} \cdot V_{IN(RMS)MIN} = \sqrt{2} \cdot 85V = 120.21 V$$

[6]

Based on the boost converter voltage conversion ratio:

$$D = \frac{(V_O - V_{IN(PK)MIN})}{V_O} = \frac{(395 - 120.21)}{395} = 0.717$$

[7]

The boost inductance is then given by:

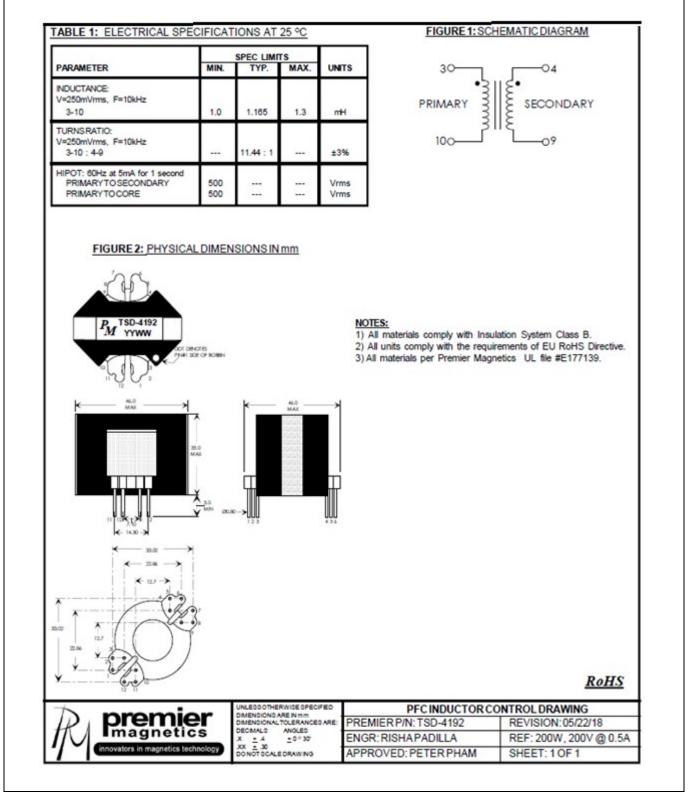

$$L_{BOOST} = \frac{V_{IN(PK)MIN} D}{F_{SW} \Delta I_L} = \frac{120.21 \ V \cdot \ 0.717}{70k \cdot \ 0.939A} = 1.165 \ mH$$

[8]

A value of 1.2 mH is selected for  $L_{BOOST}$  for this converter.

#### 3. High-frequency input capacitor

The purpose of the High-Frequency (HF) capacitor is to supply the HF component of the inductor current (the ripple component) via the shortest possible loop. This has the advantage of acting like an EMI filter since it minimizes the HF current requirement from the AC-line. Typically a HF film capacitor with low ESL and high-voltage rating (630 V) is used.

HF input capacitor design is essentially a trade-off between:

- Sizing it sufficiently to minimize the noise injected back into the AC-line

- Making it small enough to avoid line current zero-crossing distortion (flattening)

The HF input capacitor is determined as follows:

$$C_{IN} = k_{\Delta I_L} \cdot \frac{I_{IN(RMS)MAX}}{2.\pi \cdot F_{SW} \cdot r \cdot V_{IN(RMS)MIN}}$$

Where:

$k_{\Delta I_L}$ = inductor current ripple factor of 20 percent, as mentioned earlier r = maximum HF input voltage ripple factor ( $\Delta V_{IN}/V_{IN}$ ), assumed 6 percent

$$C_{IN} = k_{\Delta I_L} \cdot \frac{I_{IN(RMS)MAX}}{2.\pi \cdot F_{SW} \cdot r \cdot V_{IN(RMS)MIN}} = 0.25 \cdot \frac{2.662}{2.\pi \cdot 70k \cdot 6\% \cdot 85} = 296.7nF$$

A standard 330 nF, 630 V capacitor is selected for  $C_{IN}$  for this converter.

4. Output capacitor

$$(C_{OUT})$$

[9]

#### PFC boost stage dimensioning

Output capacitor sizing is based on the hold-up time requirement. For 20 ms hold-up time and minimum output voltage of 300 V the output capacitance is first calculated:

$$C_{OUT(MIN)} = \frac{2.P_0.\Delta t}{V_0^2 - V_{O(MIN)}^2} = \frac{2.210.0.02}{395^2 - 350^2} = 250.6 \,\mu F$$

[10]

Minimum capacitor value must be de-rated for capacitor tolerance (20 percent) to guarantee the minimum hold-up time.

$$C_{OUT} = \frac{C_{OUT(MIN)}}{1 - \Delta C_{TOL}} = \frac{250.6 \cdot 10^{-6}}{1 - 20\%} = 313 \,\mu F$$

[11]

Based on the board testing done in the lab, a standard 180  $\mu$ F, 450 V capacitor was sufficient for 20 ms hold-up time. RMS capacitor rating is:

$$I_{Crms} = I_{out} \cdot \sqrt{\frac{16 \cdot V_{out}}{3.\pi \cdot V_{acmin(dc)}} - 1} = 1.138 \, A$$

[12]

IR1155S control circuit design

## 7 IR1155S control circuit design

### 7.1 CS resistor (ISNS pin)

The IR1155S incorporates two levels of current limiting:

- 1. A "soft" current limit, which limits the duty cycle and causes the DC bus voltage to fold back, i.e. droop

- 2. A cycle-by-cycle "peak" current limit feature, which immediately terminates the current gate drive pulse once the ISNS pin voltage exceeds the V<sub>ISNS(PK)</sub> soft current limit

The COMP pin voltage is directly proportional to the RMS input current into the PFC converter, i.e.  $V_{COMP}$  is higher at higher RMS current. Clearly its magnitude is highest at maximum load  $P_{MAX}$  and minimum AC input voltage,  $V_{IN(MIN)}$ . The dynamic range of  $V_{COMP}$  is defined by  $V_{COMP(EFF)}$  stated in the IR1155S datasheet. Once the  $V_{COMP}$  signal reaches  $V_{COMP(EFF)}$  any system requirement causing an additional increase in current will cause the IC to respond by limiting the duty cycle and thereby causing the output voltage to drop. This is called "soft" current limit protection. The selection of  $R_{SNS}$  must ensure that soft current limit is not encountered at any of the allowable line and load conditions.

#### 1. R<sub>SNS</sub> calculation

The determination of  $R_{SNS}$  is performed at the system condition when the inductor current is highest at lowest input line ( $V_{IN(MIN)}$ ) and highest load ( $P_{MAX}$ ). The inductor current is highest at the peak of the AC sinusoid. The duty cycle required at the peak of AC sinusoid at  $V_{IN(MIN)} = 85$  V AC in order to regulate  $V_{OUT} = 388$  V is:

$$D_{PEAK} = \frac{(V_O - \sqrt{2}V_{IN(RMS)MIN})}{V_O} = \frac{(395 - \sqrt{2} \cdot 85)}{395} = 0.696$$

[13]

$R_{\mbox{\tiny SNS}}$  selection should guarantee that:

- i. PFC algorithm can deliver this duty cycle at the peak of AC sinusoid at V<sub>IN(MIN)</sub> and P<sub>MAX</sub> condition

- ii. Soft current limit is encountered whenever there is a further increase in demand for current while operating at V<sub>IN(MIN)</sub> and P<sub>MAX</sub> condition. To do this, V<sub>ISNS</sub> is calculated below:

$$V_{ISNS(MAX)} = \frac{V_{COMP(EFF)MIN}(1-D)}{g_{DC}} = \frac{4.6V \cdot (1-0.696)}{3.1} = 0.452 V$$

[14]

Note: If the calculated  $V_{ISNS(MAX)}$  is higher than the cycle-by-cycle peak over-current limit threshold of the IC, the  $V_{ISNS(PK)}$  value should be used to determine  $R_{SNS}$ . In this example,  $V_{ISNS(MAX)}$  is lower than the minimum  $V_{ISNS(PK)}$  value specified in the datasheet (0.69 V), thus 0.47 V is used for  $R_{SNS}$  calculation.

Next the peak inductor current at maximum peak AC-line current, de-rated with an over-load factor (KOVL of 5 percent), is calculated.

$$I_{IN(PK)OVL} = I_{L(PK)MAX} (1 + K_{OVL}) = 4.227 (1 + 0.05) = 4.438 A$$

[15]

From this maximum current level and the required voltage on the CS pin, the maximum resistor value that can be used for the PFC converter is determined.

$$R_{SNS} = \frac{V_{SNS(MAX)}}{I_{IN(PK)OVL}} = \frac{0.452}{4.438} = 0.102 \ \Omega$$

[16]

[18]

IR1155S control circuit design

It is noted that even although IR1155S operates in average current mode it is still safer to use the peak inductor current for CS resistor design to guarantee avoidance of premature fold-back.

Power dissipation in the resistor is now calculated based on worst case RMS input current at minimum input voltage:

$$P_{RS} = I_{IN(RMS)MAX}^2, R_s = 2.662^2, 0.102 = 0.721 W$$

[17]

A standard 0.1  $\Omega/3$  W resistor is selected for  $R_{SNS}$ , keeping in mind the inrush current at the initial turnon of the power supply.

#### 2. Peak current limit

The cycle-by-cycle peak current limit is reached when the  $V_{ISNS}$  pin voltage exceeds  $V_{ISNS(PK)}$ . For the PFC converter this limit is encountered whenever the inductor current exceeds the following:

$$I_{PK\_LMT} = \frac{|-0.77|}{0.1} = 7.549 \,A$$

It is clear that even though the IR1155S operates based on average current mode control, the input to the peak current limit comparator is decoupled from the averaging circuit, thus enabling instantaneous cycle-by-cycle protection for peak over-current.

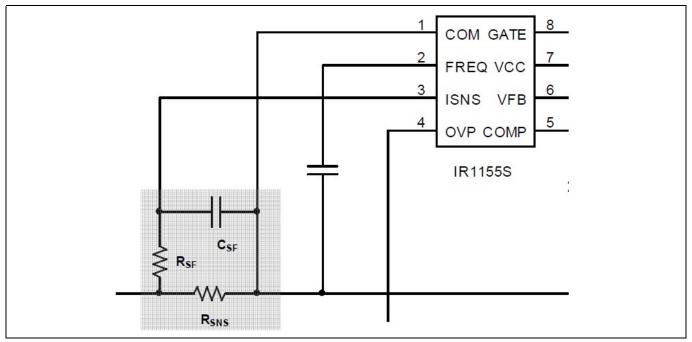

Figure 13 CS resistor and filtering

The CS signal is detected at the  $I_{SNS}$  pin of the IC using a current-limiting series resistor,  $R_{SF}$ . An external RC filtering for the  $I_{SNS}$  pin can be realized (though not necessarily for IR1155S) by adding a filter capacitor  $C_{SF}$  between the  $I_{SNS}$  pin and COM, as shown in figure 13. A corner frequency around 1 to 1.5 MHz will offer a safe compromise in terms of filtering, while maintaining the integrity of the CS signal for cycle-by-cycle peak OCP.

$$F_{PSF} = \frac{1}{2 \cdot \pi \cdot R_{SF} \cdot C_{SF}}$$

[19]

IR1155S control circuit design

With  $R_{sF} = 100 \Omega$ , we can use  $C_{sF} = 1 \text{ nF}$  to obtain a cross-over frequency of 1.6 MHz. The input impedance of the CS amplifier is approximately 25 k $\Omega$ . The  $R_{sF}$  resistor will form a divider with this 25 k $\Omega$  resistor. For  $R_{sF} = 100 \Omega$  it is noted that the accuracy of the CS voltage signal communicated to the IC is more than 99.5 percent.

#### 3. Output regulation voltage divider (VFB pin)

The output regulation voltage of the PFC converter is set by voltage divider at the VFB pin ( $R_{FB1}$ ,  $R_{FB2}$  and  $R_{FB3}$ ). The total impedance of this divider network must be high enough to reduce power dissipation but low enough to keep the feedback voltage error (due to finite bias currents into the voltage error amplifier, which is less than 0.2 µA) negligible. Around 2 M $\Omega$  is an acceptable value for the total resistor divider impedance. A standard 499 k $\Omega$ , 1 percent tolerance resistor is selected for  $R_{FB1}$  and  $R_{FB2}$  for this converter. Then,  $R_{FB3}$  is determined based on error amplifier  $V_{REF(TYP)} = 5$  V and  $V_{OUT} = 388$  V converter specification:

$$R_{FB3} = V_{REF} \cdot \frac{(R_{FB1} + R_{FB})}{(V_{\text{OUT}} - V_{REF})} = 5 \cdot \frac{(499 \, k + 499 \, k)}{(395 - 5)} = 12.79 \, k\Omega$$

[20]

A standard resistor,  $R_{FB3}$  = 13.0 k $\Omega$ , 1 percent tolerance, is selected for this converter.

Power dissipation of divider resistors is given by the following.

$$P_{R_{FB1}} = P_{R_{FB}} = \frac{(V_O - V_{REF})^2}{2.(R_{FB1} + R_{FB2})} = \frac{(395 - 5)^2}{2(499 \, k + 499 \, k)} = 76 \, mW$$

[21]

#### 4. Dedicated OVP divider (OVP/EN pin)

The IR1155S features a dedicated over-voltage sensing input pin (OVP/EN). The user can use the same resistor divider as calculated earlier with FB control. This will give a fixed OVP level, which is 106.5 percent of regulated output voltage. If a different over-voltage level is desired, a separated OVP resistor divider can be calculated. Here is an example:

A 499 k $\Omega$ , 1 percent tolerance resistor is selected for  $R_{OVP1}$  and  $R_{OVP2}$  for this converter. The OVP threshold is 420 V:

$$R_{OVP3} = \frac{1.065 \cdot V_{REF} \cdot (R_{OVP1} + R_{OVP2})}{(V_{OV} - 1.065 \cdot V_{REF})} = 1.065 \frac{5 \cdot (499k + 487k)}{(420 - 1.065 \cdot 5)} = 12.66 \, k\Omega$$

[22]

The OVP reset point can be calculated:

$$V_{OVPREST} = \frac{1.022 \cdot V_{OV}}{1.065} = 1.022 \cdot \frac{420}{1.065} = 403.04 \, V$$

[23]

#### 5. Timing capacitor (FREQ pin)

The timing capacitor  $C_T$  can be obtained per the following formula:

$$C_T = \frac{\left(\frac{1}{F_{sw}} - 0.45\,\mu s\right).0.194\,mA}{2V} = \frac{\left(\frac{1}{70\,k} - 0.45\,\mu s\right).0.194\,mA}{2} = 1.34\,nF$$

[24]

For 70 kHz target switching frequency, C<sub>T</sub> is calculated as 1.34 nF. A standard 1.3 nF capacitor will be used, and it programs the switching frequency to 70 kHz.

IRS27952 functional overview

## 8 IRS27952 functional overview

The IRS27952 is a self-oscillating half-bridge driver IC for resonant half-bridge DC-DC converter applications for use up to 600 V. It has a fixed 50 percent duty cycle (minus the dead-time) and very wide operating frequency range able to operate up to 500 kHz. The frequency can be adjusted between two set boundaries via an opto-isolator feedback circuit. The frequency range is programmed by external components connected to the RT and CT<sup>1</sup> pins, allowing flexibility to set the minimum and maximum operating frequencies as well as the frequency sweep at power-up for the soft-start function. The dead-time is also adjustable, determined by the CT capacitor. Programmable dead-time is essential to enable the designer to optimize the system with the minimum body-diode conduction time in M2 and M3 for higher efficiency under full load, while maintaining ZVS under a no-load condition. The IRS27952 also offers OCP using the on-state resistance of the low-side MOSFET sensed at the VS pin with a nominal threshold of 3 V. The gate drive outputs can be disabled by externally pulling the voltage at the CT pin below its enable voltage threshold. In this condition the IC enters sleep mode, in which minimal power is consumed. However great care must be taken when connecting any additional protection circuitry to the CT pin. Only an open-collector type comparator is suitable with defined fully on and off states. This is because any small leakage currents present at the CT node affect the operation of the oscillator and cause unstable operation and possible MOSFET failure.

|                | Pin | Name  | Description                           |

|----------------|-----|-------|---------------------------------------|

|                | 1   | VCC   | Supply voltage                        |

| 1 VCC VB 8     | 2   | RT    | Oscillator timing resistor            |

| 2 RT 6 HO 7    | 3   | CT/SD | Oscillator timing capacitor/shut-down |

| 3 CT/SD 2 VS 6 | 4   | СОМ   | Ground                                |

|                | 5   | LO    | Low-side gate drive                   |

| 4 COM LO 5     | 6   | VS    | High-side gate drive return/HV CS     |

|                | 7   | но    | High-side gate drive                  |

|                | 8   | VB    | High-side floating supply voltage     |

Figure 14 IRS27952 pin assignment

<sup>&</sup>lt;sup>1</sup> CT refers to the capacitor connected to the CT/SD pin of the IRS27952 (see figure 14), not to be confused with CT of the IR1155 referred to in the previous section.

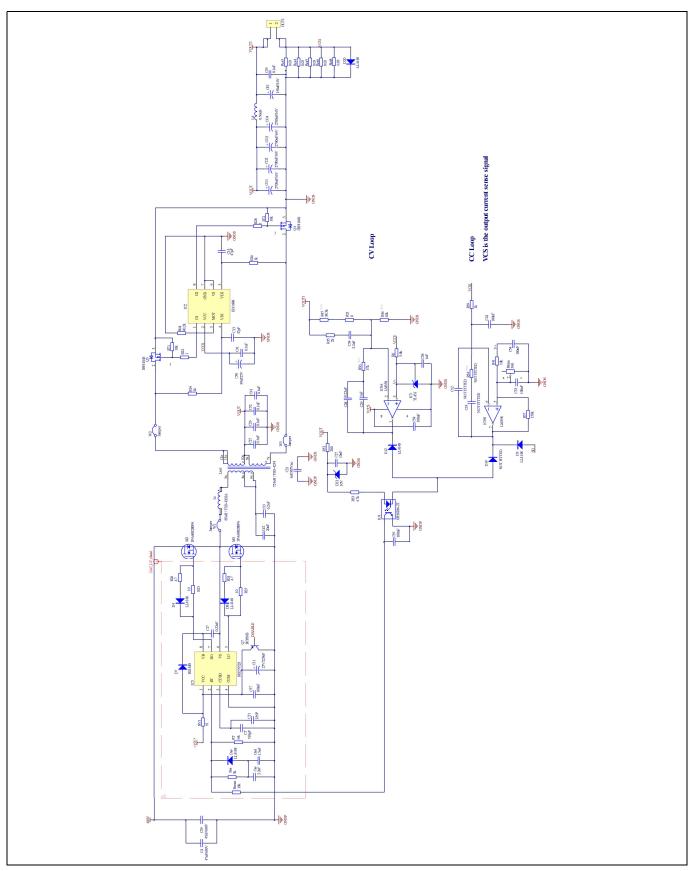

## 9 LLC resonant half-bridge converter operation

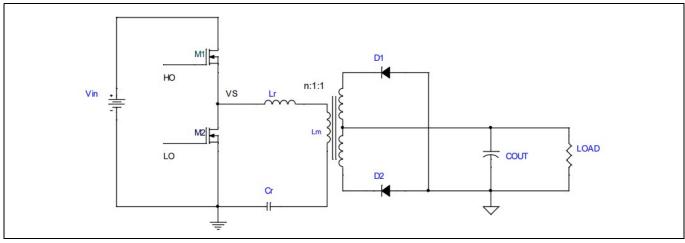

The increasing popularity of the LLC resonant converter in its half-bridge implementation is due to its highefficiency, low switching noise and ability to achieve high power density. This topology is also the most attractive topology for front-end DC bus conversion. It utilizes the magnetizing inductance of the transformer to construct a complex resonant tank with buck and boost transfer characteristics in the soft-switching region. The typical power stage schematic for this topology is shown below:

Figure 15 LLC resonant half-bridge converter basic elements

Devices M1 and M2 operate at 50 percent duty cycle, and the output voltage is regulated by varying the switching frequency of the converter. The converter has two resonant frequencies: a lower resonant frequency (given by  $L_m$ ,  $L_r$ ,  $C_r$  and the load), and a fixed higher-series resonant frequency  $F_{r1}$  (given by  $L_r$  and  $C_r$  only). The two bridge devices M1 and M2 can be soft-switched for the entire load range by operating the converter under inductive load mode (ZVS region). It can be either above or below the resonant frequency  $F_{r1}$ .

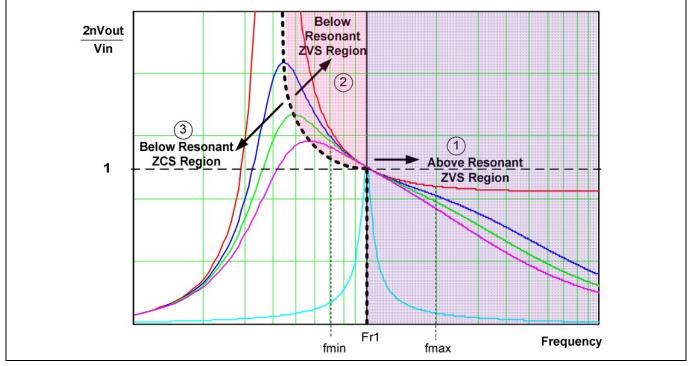

Figure 16 Frequency response of a typical LLC resonant converter

The characteristics of an LLC resonant converter can be divided into three regions based on the three different modes of operation. The first region is for a switching frequency above the resonant frequency F<sub>r1</sub>:

$$F_{r1} = \frac{1}{2.\pi . \sqrt{L_r . C_r}}$$

[25]

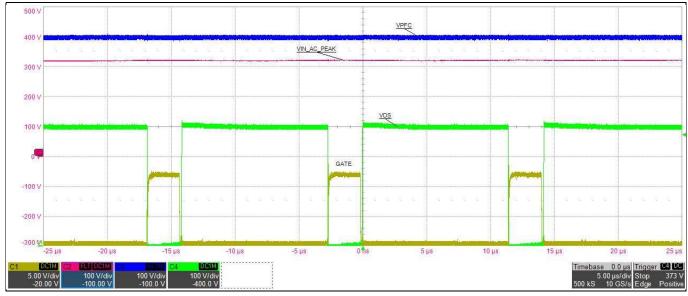

In region 1 of figure 16 (the purple shaded area) the switching frequency is higher than resonant frequency F<sub>r1</sub>. The converter operation is very similar to a series resonant converter. Here L<sub>m</sub> does not resonate with the resonant capacitor C<sub>r</sub>; it is clamped by the output voltage and acts as the load of the series resonant tank. This is the inductive load region and the converter is always under ZVS operation regardless of the load condition.

In region 2 (the pink shaded area) the switching frequency is higher than the lower resonant frequency but lower than  $F_{r1}$ . The lower resonant frequency varies with load so the boundary (the dotted line of the load gain curve) of region 2 and region 3 traces the peaks of the family of load vs. gain curves. In this complex region the LLC resonant operation can be divided into two time intervals; in the first time interval  $L_r$  resonates with  $C_r$  and  $L_m$  and is clamped by the output voltage. When the current in the resonant inductor  $L_r$  resonates back to the same level as the magnetizing current,  $L_m$  and  $C_r$  stop resonating.  $L_m$  now participates in the resonant operation and the second time interval begins. During this time interval the dominant resonant components become  $C_r$ and  $L_m$  in series with  $L_r$ . The ZVS operation in region 2 is guaranteed by operating the converter to the right side of the load gain curve. For a switching frequency below resonant frequency  $F_{r1}$  operation could fall in either region 2 or region 3 depending on the load condition.

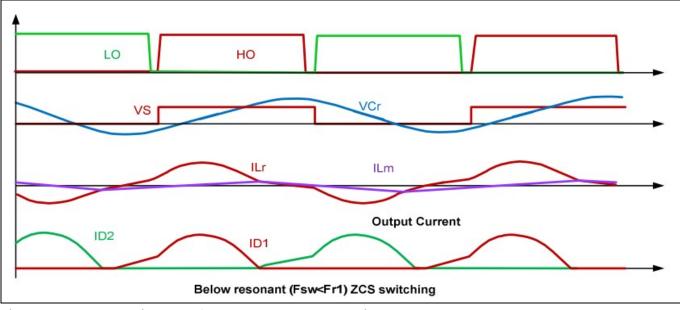

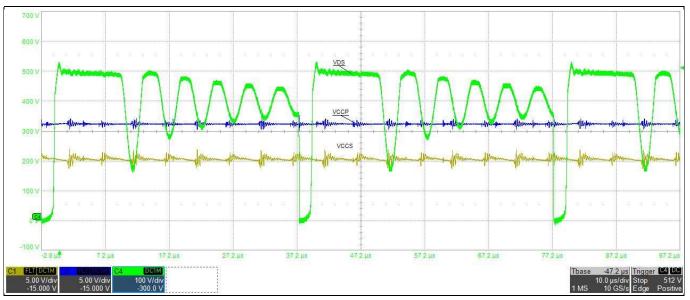

The waveforms in figures 17, 18, 19 and 20 show the behavior of the system in each of the operating regions.

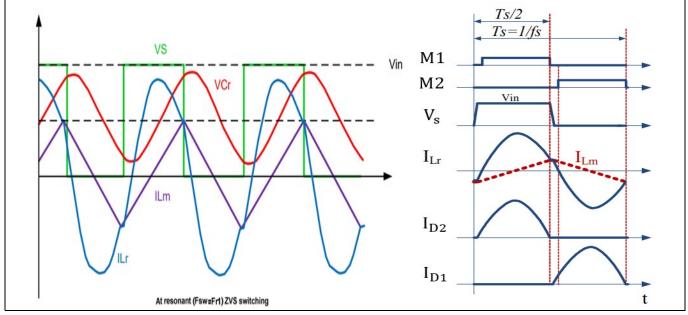

Figure 17 Operating waveforms at resonance with ZVS

When operating at resonance ( $F_{sw} = F_{r1}$ ), each half switching cycle ( $T_s/2$ ) contains a complete power delivery. During the first time interval  $T_s/2$ ,  $L_r$  resonates with  $C_r$  and  $L_m$  is clamped by the output voltage and acts as the load of the series resonant tank. When the current in the resonant inductor  $L_r$  resonates back to the same level as the magnetizing current  $L_m$ , the  $L_r$  and the  $C_r$  stop resonating and  $L_m$  now participates in the resonant operation and the second time interval begins. During this time interval the dominant resonant components are  $C_r$  and  $L_m$  in series with  $L_r$ . At this time, the rectifier current in the secondary side of the transformer reaches zero. At this point the resonant tank has unity gain with optimum efficiency, and therefore the transformer turns ratio is designed such that the converter operates at this point at nominal input and output voltages.

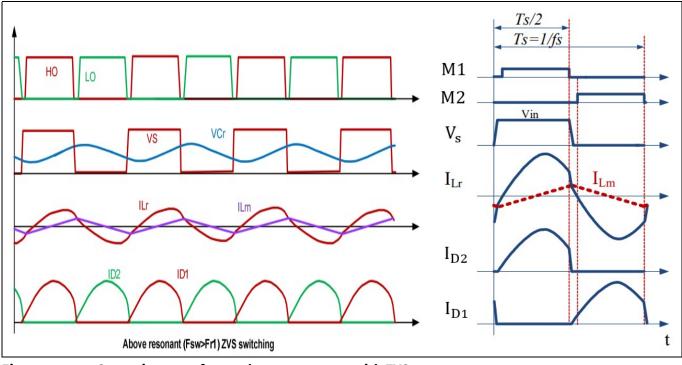

Figure 18 Operating waveforms above resonance with ZVS

Figure 18 shows the operation above the resonant frequency. Each half of the switching cycle contains a partial power delivery since the resonant half-cycle is not completed and is interrupted by the start of the other half of the switching cycle. The primary-side MOSFETs have therefore increased turn-off losses and secondary rectifier diodes are subject to hard commutation [3]. The converter operates in this mode at higher input voltage where a step-down gain or buck operation is required.

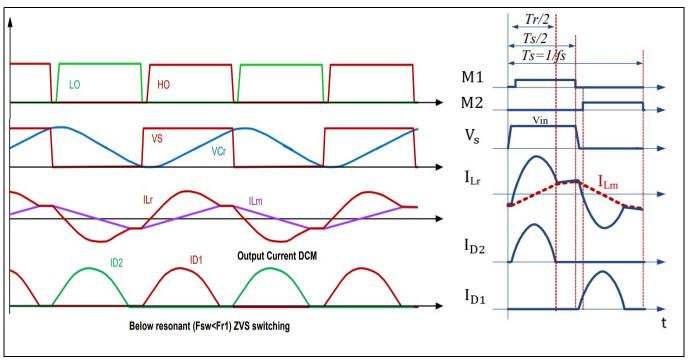

Operating below resonance, each half of the switching cycle contains a power delivery operation. At the time when the resonant half-cycle has completed and resonant inductor current  $I_{Lr}$  reaches the magnetizing current, the freewheeling operation starts and carries on to the end of the switching half-cycle. The primary side now sees increased conduction losses due to the circulating energy. The converter operates in this mode at lower input voltage, where a step-up gain or boost operation is required. The waveforms shown in figure 19 indicate that the secondary rectifier diode currents transition from CCM to DCM when the switching frequency changes from above resonant ZVS to below resonant ZVS due to increasing load. The ripple voltage on the resonant capacitor  $C_r$  also increases in the below-resonant ZVS mode.

Figure 20 Operating waveforms below resonance with ZCS

In the ZCS region ( $F_{sw}$  less than  $F_{r1}$ ), the LLC resonant converter operates in capacitive mode, and M1 and M2 are hard switching with high switching losses. For this reason ZCS operation should always be avoided.

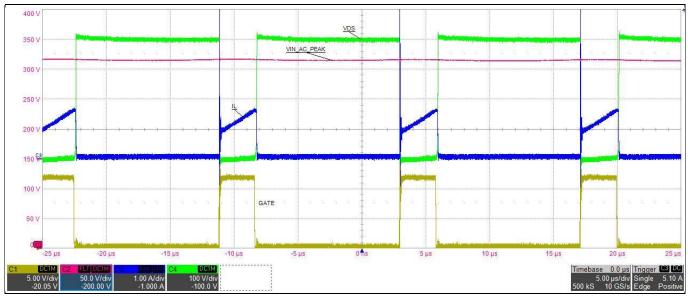

### 9.1 Important points to consider when designing an LLC converter

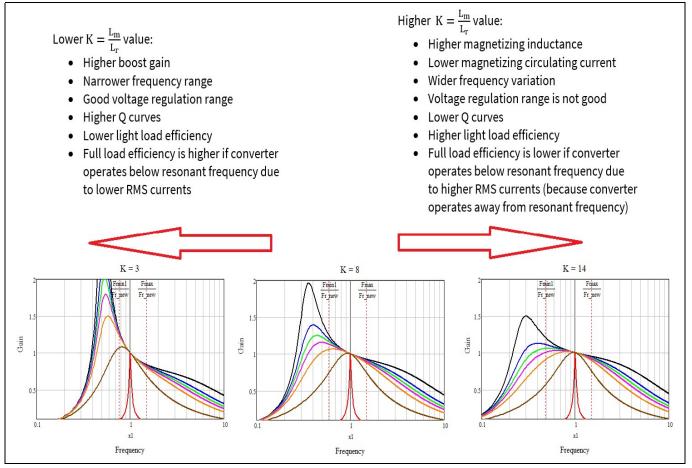

- As k (L<sub>m</sub>/L<sub>r</sub> ratio) increases, I<sub>Lm</sub> decreases, Q decreases, voltage stress on C<sub>r</sub> (V<sub>cr(pk-pk)</sub>) is reduced, deadtime increases, no/light-load current decreases, light-load efficiency increases and frequency range increases.

- 2) Increasing k causes the gain peak to drop so the voltage regulation range is reduced because the frequency span increases.

- 3) Keeping the values of  $L_m$  and  $C_r$  unchanged and decreasing  $L_r$  reduces the gain.

- 4) When the switching frequency is lower than the resonant frequency, behavior is more like a parallel resonant converter with higher gain but with higher circulating currents (peak and RMS currents are higher). The conduction losses in the half-bridge MOSFETs and transformer are therefore higher. On the secondary side the synchronous rectifier MOSFETs will have ZVS turn-on and ZCS turn-off.

- 5) When the switching frequency is higher than the resonant frequency, the primary peak and RMS currents in the tank are lower. However, on the secondary side the rectifier MOSFET turns off with non-zero current, resulting in hard switching, so the reverse recovery (Q<sub>rr</sub>) of the MOSFET shows up as a large ringing spike on the V<sub>DS</sub> waveform.

For wide voltage range, narrow switching frequency is needed, which means lower k ratio and lower  $L_r/C_r$ . Efficiency versus voltage regulation range is a trade-off.

LLC resonant half-bridge converter operation

Figure 21 Gain curves for different values of k

A study by Infineon<sup>1</sup> compared a 600 W LLC design for k = 6 and k = 13. Both converters were operating below the resonant frequency. The light-load efficiency was higher, with k = 13 due to lower magnetizing current, but the full-load RMS current was higher, which translated to a lower efficiency at full load. Full-load RMS currents are higher because the frequency range is wider, with k = 13 and converter operating away from resonant frequency. With k = 6, the full-load RMS current is lower, therefore efficiency is higher at full load than with k =13. This is because the frequency range is narrower and the converter operates close to the resonant frequency. The light-load efficiency with k = 6 was lower than k = 13 due to high circulating currents in the resonant tank.

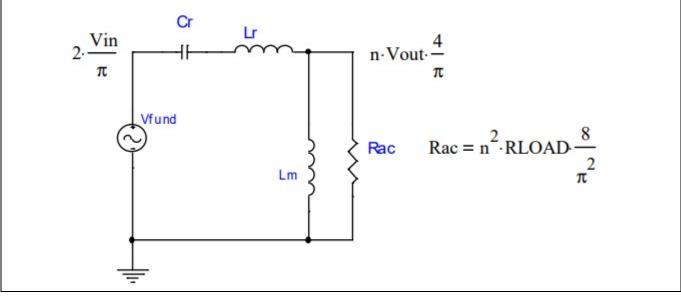

### 9.2 First Harmonic Approximation (FHA)

To design the LLC resonant half-bridge resonant converter, the First Harmonic Approximation (FHA) is used to obtain an equivalent circuit. All the components are referenced to the primary side to simplify the analysis. The load is equated to a resistor  $R_{ac}$ , which is situated in parallel with transformer primary inductance  $L_m$ .

The equivalent AC resistor is given by:

$$R_{ac} = \frac{8n^2}{\pi^2} R_{Load}$$

[26]

<sup>&</sup>lt;sup>1</sup> Study carried out by Jon Hancock and Mladen Ivankovic Application Note

LLC resonant half-bridge converter operation

#### Figure 22 FHA equivalent circuit

The transfer ratio of the equivalent circuit can be obtained as follows:

$$M = \left| \frac{\frac{j.\omega.L_m.R_{ac}}{j.\omega.L_m+R_{ac}}}{j.\omega.L_r + \frac{1}{j.\omega.C_r} + \frac{j.\omega.L_m.R_{ac}}{j.\omega.L_m+R_{ac}}} \right|$$

[27]

**Resonant frequency**

*M* can be broken down as follows:

$$F_{r1} = \frac{1}{2\pi\sqrt{L_rC_r}}$$

$$x = \frac{F_{S\omega}}{F_{r1}}$$

$$k = \frac{L_m}{L_r}$$

$$R_{ac} = \frac{8 \cdot n^2 \cdot R_{load}}{\pi^2}$$

$$n = \frac{N_p}{N_s}$$

$$Q = \frac{2 \cdot \pi \cdot F_{r1} \cdot Lr}{R_{ac}} = \frac{1}{2 \cdot \pi \cdot F_{r1} \cdot Cr \cdot R_{ac}}$$

Normalized switching frequency Ratio of magnetizing inductance to resonant inductance Reflected load resistance

Turns ratio

**Quality factor**

$$M = \left| \frac{1}{1 + \frac{1}{k} \cdot \left(1 - \frac{1}{x^2}\right) + j \cdot Q \cdot \left(x - \frac{1}{x}\right)} \right|$$

$$M = \frac{1}{\sqrt{\left[1 + \frac{1}{k} \cdot \left(1 - \frac{1}{x^2}\right)\right]^2 + \left[Q \cdot \left(x - \frac{1}{x}\right)\right]^2}}$$

Or

[28]

LLC resonant half-bridge converter operation

The conversion ratio of output voltage  $V_{OUT}$  to input voltage  $V_{IN}$  is given by:

| Vout     | _ | Μ    |  |

|----------|---|------|--|

| $V_{in}$ | _ | 2 .n |  |

[29]

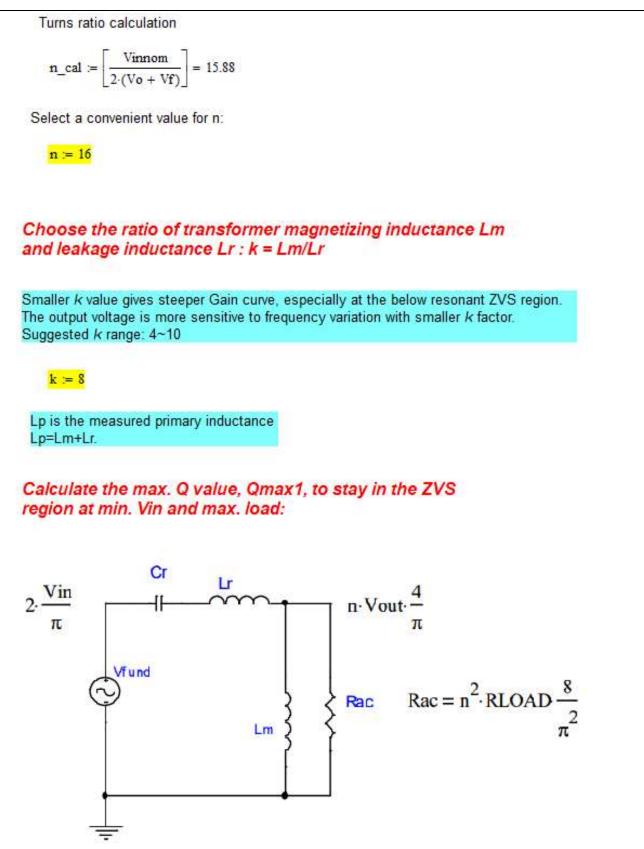

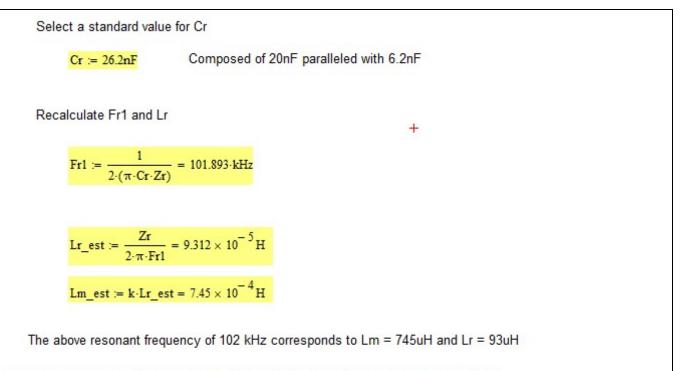

Design calculations for the DEMO\_200W\_12VDC\_LLC HB resonant DC-DC stage have been made using MathCAD 15 software, which will be listed in the following pages.

LLC resonant half-bridge converter operation

#### Code Listing 1

| Design of L          | <u>C Resonant Half-Bridge</u>                  |       |

|----------------------|------------------------------------------------|-------|

| Input Parame         | ters:                                          |       |

| Input Voltage:       |                                                |       |

| Vinn                 | in := 350V Vinnom := 397V Vinmax := 420V       |       |

| Output Voltage       |                                                |       |

| Vo >                 | = 12V Vf := 0.5V Vf with sync rec may be lower |       |

| Output Curren        |                                                |       |

| Io := 16A            |                                                |       |

| Po := Vo·I           | o = 192 W                                      |       |

|                      | operation freq range:                          |       |

| resonant frequ       | ency (Fr), and max_frequency (Fmax)            |       |

| Fr := 100k           | Hz Fmax := 150kHz                              |       |

| Load resist          | ansformer turns-ratio n per maximum input vol  | ltage |

|                      |                                                |       |

| $RL := \frac{V}{Ic}$ | $P = 0.75 \Omega$                              |       |

| Mmin, Mno            | m, Mmax are the gains                          |       |

| Mmin := (            | $\frac{Vo + Vf}{Vinmax} = 0.03$                |       |

| Mnom :=              | $\frac{(Vo + Vf)}{Vinnom} = 0.031$             |       |

| Mmax :=              | $\frac{Vo + Vf}{Vinmin} = 0.036$               |       |

|                      |                                                |       |

$xmax := \frac{Fmax}{Fr} = 1.5$

LLC resonant half-bridge converter operation

#### **Code Listing 2**

#### **Code Listing 3**

Transfer ratio of the equivalent circuit can be obtained as following:

The power stage gain is:

The M(x,k,Q)=

$$\frac{1}{\sqrt{\left[1+\frac{1}{k}\cdot\left(1-\frac{1}{x^2}\right)\right]^2+Q^2\cdot\left(x-\frac{1}{x}\right)^2}}$$

To keep the converter working in soft switching mode, the operating point should always lie in the ZVS region as shown in gain curve. The ZVS-ZCS boundary line is defined by the phase angle of Zin,  $\Phi(Zin)=0$  (the boundary condition between capacitive and inductive load), i.e. the imaginary part of Zin is zero. With this condition we can calculate the maximum Q, which enables the converter to remain in ZVS. The maximum Q occurs at the minimum input voltage and the maximum load.

Input impedance:

$$Zin = Zr \left| \frac{k^2 \cdot x^2 \cdot Q}{1 + k^2 \cdot x^2 \cdot Q^2} + j \left( x - \frac{1}{x} + \frac{x \cdot k}{1 + k^2 \cdot x^2 \cdot Q^2} \right) \right|$$

The definition of k, x and Q:

$$Fr1 = \frac{1}{2\pi\sqrt{Lr\cdot Cr}} \qquad \qquad Q = \frac{\sqrt{\frac{Lr}{Cr}}}{Rac}$$

Calculate Qmax to remain in ZVS operation at maximum load and minimum input voltage. The ZVS-ZCS boarderline is defined by Im(Z(in))=0, thus:

$$Q_{\max} := \frac{1}{k} \cdot \frac{1}{2 \cdot n \cdot M_{\max}} \cdot \sqrt{\frac{(2 \cdot n \cdot M_{\max})^2}{(2 \cdot n \cdot M_{\max})^2 - 1}} + k = 0.383$$

+

#### **Code Listing 4**

$$\operatorname{Rac} := \frac{\$}{\pi^2} \cdot n^2 \cdot \operatorname{RL} = 155.629 \,\Omega$$

Set value for Q:

Q := Qmax = 0.383

## Calculate the value xmin the converter will work at, at min. input voltage and max. load:

The minimum switching frequency occurs at the maximum load and minimum input voltage with the previously calculated maximum Qmax. As Qmax is defined by Im(Zin) = 0,

$$\left[x - \frac{1}{x} + \left(x \cdot \frac{k}{1 + k^2 \cdot x^2 \cdot Qmax^2}\right) = 0\right]$$

Fmin is calculated as :

$$\operatorname{xmin} := \sqrt{\frac{1}{1 + k \cdot \left[1 - \frac{1}{(2 \cdot n \cdot \operatorname{Mmax})^2}\right]}} = 0.59$$

Fmin := xmin·Fr = 58.977·kHz

#### Calculate the characteristic impedance of the tank circuits and all component values:

$$Zr := Rac \cdot Q = 59.617 \Omega$$

$$Cr_cal := \frac{1}{2 \cdot \pi \cdot Fr \cdot Zr} = 2.67 \times 10^{-8} F$$

Lr cal :=  $\frac{Zr}{2r} = 9.488 \times 10^{-5} H$

$$Lr_cal := \frac{1}{2 \cdot \pi \cdot Fr} = 9.488 \times 1$$

LLC resonant half-bridge converter operation

#### **Code Listing 5**

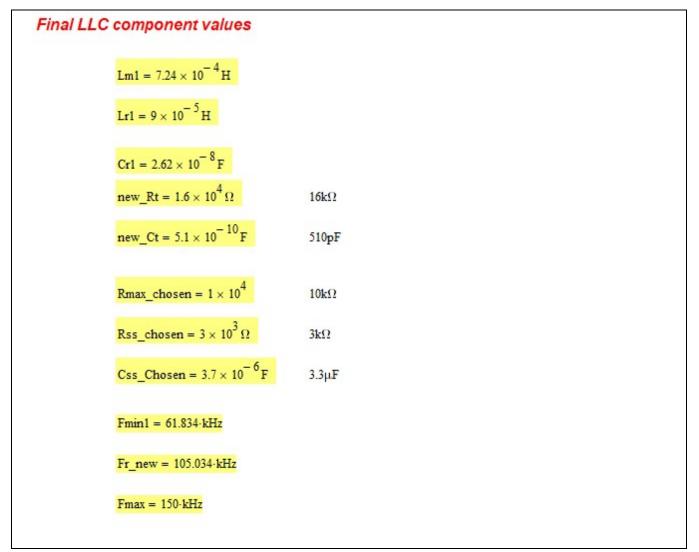

Magnetics vendor may not provide exact values as shown by the calculation above, in such cases adjust "k" and "Cr" values to match the magnetics vendor values for Lm and Lr

The LLC transformer (Lm) and resonant inductor (Lr) available with us are : Lm = 724uH and Lr = 90uH

Back calculate with the available transformer (Lm) and inductor (Lr) values

Vinmin = 350 V

Mmax1 :=

$$\frac{(Vo + Vf)}{Vinmin} = 0.036$$

Rac = 155.629  $\Omega$

n = 16

Lm1 :=  $724 \cdot 10^{-6}$ H

Lr1 :=  $90\mu$ H

Cr1 := Cr =  $2.62 \times 10^{-8}$ F

k1 :=  $\frac{Lm1}{Lr1} = 8.044$

#### **Code Listing 6**

$$Q1 := \frac{1}{k1} \cdot \frac{1}{2 \cdot n \cdot \text{Mmax1}} \cdot \sqrt{\frac{(2 \cdot n \cdot \text{Mmax1})^2}{(2 \cdot n \cdot \text{Mmax1})^2 - 1}} + k1 = 0.382$$

$Zr1 := Rac \cdot Q1 = 59.395 \Omega$

With the current Lm = 724uH and Lr= 90uH values, the new resonant frequency is

$$Fr\_new := \frac{Zr1}{(2 \cdot \pi \cdot Lr1)} = 105.034 \cdot kHz$$

$$xmin1 := \sqrt{\frac{1}{1 + k1 \cdot \left[1 - \frac{1}{(2 \cdot n \cdot Mmax1)^2}\right]}} = 0.589$$

Minimum frequency is

Fmin1 := xmin1 Fr\_new = 61.834 kHz

.

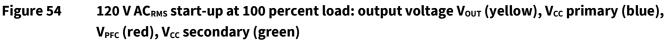

### Primary and Secondary Peak, RMS currents

I1 is the current where the resonant current in Lr meets the magnetizing current in Lm. This is also the point where Cr and Lr finish resonance for the first half-period of Fr1. At this point, there is no more energy delivered to the load and the output diodes are off. The Cr starts to resonate with Lr + Lm until the switching MOSFETs change states. I1 can be calculated as:

$$Lm1 = 7.24 \times 10^{-4} H$$

$$Fr_new = 105.034 \cdot kHz$$

$$I1 := n \cdot \frac{Vo}{2 \cdot Lm1 \cdot 2 \cdot Fr_new} = 0.631 A$$

$$Fmin1 = 61.834 \cdot kHz$$

$$Fr_new = 105.034 \cdot kHz$$

$$Fmax = 150 \cdot kHz$$

$$Io = 16 A$$

LLC resonant half-bridge converter operation

$$Ipri_p k := \sqrt{\left(I_0 \cdot \frac{\pi}{2 \cdot n}\right)^2 + I1^2} = 1.693 \text{ A}$$

$$Ispk := I_0 \cdot \frac{\pi}{2} = 25.133 \text{ A}$$

$$Iprms := \frac{Ipri_p k}{\sqrt{2}} = 1.197 \text{ A}$$

$$Isrms := I_0 \cdot \frac{\pi}{4} = 12.566 \text{ A}$$

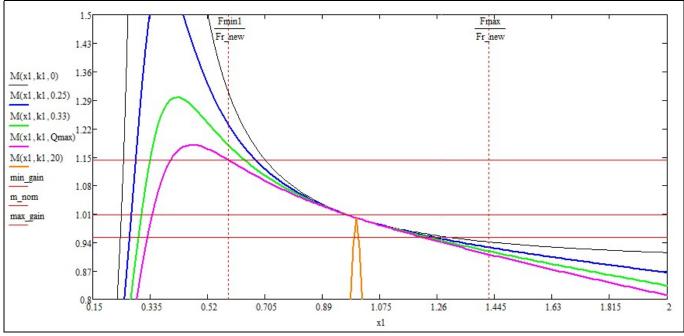

Plot the power stage transfer function per Lr, Lm, Cr, Rac :

$$M(x1, k1, Q1) := \left| \frac{1}{\sqrt{\left[1 + \frac{1}{k1} \cdot \left(1 - \frac{1}{x1^2}\right)\right]^2 + Q1^2 \cdot \left(x1 - \frac{1}{x1}\right)^2}} \right|$$

$$x1 := 0.1, 0.11..10 \quad k1 = 8.044 \quad Q1 = 0.382 \quad n = 16$$

$$Virmin = 350V \qquad Vinnom = 397V \qquad Vinmax = 420V \quad Vf = 0.5V$$

$$min_gain := 2 \cdot n \frac{(V_0 + Vf)}{Vinmax} = 0.952$$

$$m_nom := 2 \cdot n \frac{(V_0 + Vf)}{Vinmin} = 1.008$$

$$max_gain := 2 \cdot n \frac{(V_0 + Vf)}{Vinmin} = 1.143$$

Fmin1 = 61.834 kHz Fr\_new = 105.034 kHz Fmax = 150 \text{ kHz}

Figure 23 Curves of gain against frequency

The above graph is based on FHA. It shows the variation of the gain versus the frequency. The pink curve corresponds to the full-load condition ( $Q = Q_{max} = 0.383$ ). In order to design the LLC tank components for optimized operation over an input PFC voltage variation of 350 V up to 420 V, it is necessary to make sure the no-load (Q = 0, black) and the full-load ( $Q = Q_{max}$ , purple) curves intersect the minimum gain (min\_gain = 0.952), nominal gain (m\_nom = 1.008) and the maximum gain (max\_gain = 1.143) shown on the vertical axis, within the frequency boundaries.

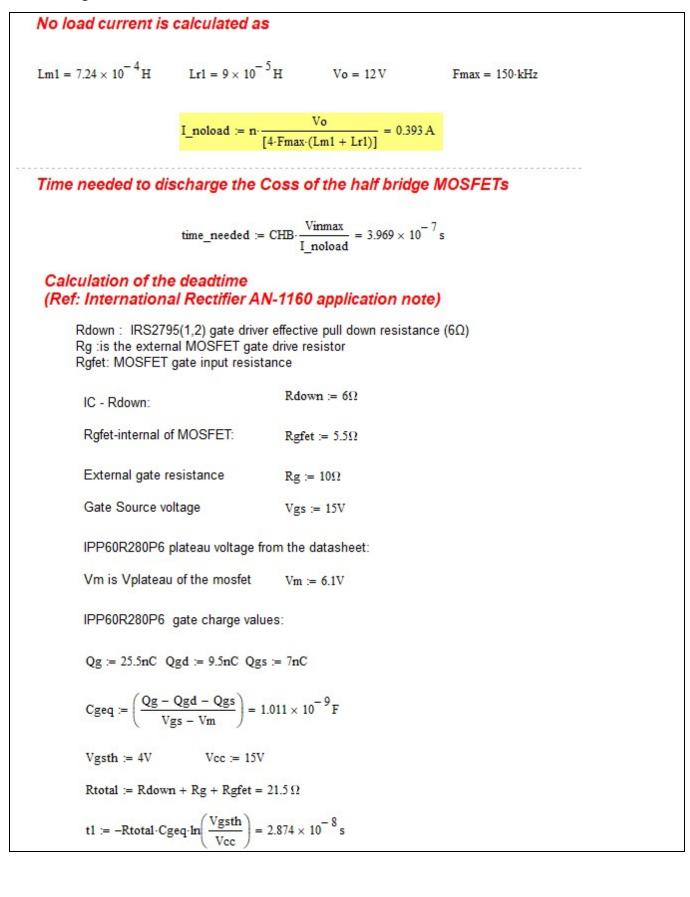

### 9.3 Dead-time calculations

### **Code Listing 8**

What happens during the dead time ? n = 16  $Lm1 = 7.24 \times 10^{-4} H$  $Lr1 = 9 \times 10^{-5} H$  $Cr1 = 2.62 \times 10^{-8} F$ IPP60R280P6 MOSFET parameters: Rdson :=  $280 \cdot 10^{-3} \Omega$  factor := 1.76 Fmax =  $150 \cdot kHz$ Co\_er is the energy related capacitance when Vds is rising from 0 to 400V: Co er := 44pF Vds := 400V Idoff\_min :=  $2 \cdot \frac{\sqrt{2}}{\pi} \cdot n \cdot \frac{Vo}{2 \cdot \pi \cdot Fmax \cdot Lm1} = 0.253 \text{ A}$ Ceq :=  $2 \cdot Co_{er} = 8.8 \times 10^{-11} F$ First Condition Inductive energy > Capacitive energy  $\frac{1}{2} \cdot (\text{Lm1} + \text{Lr1}) \cdot \text{Idoff}_{\text{min}}^2 = 2.612 \times 10^{-5} \text{J} \qquad \qquad \frac{1}{2} \cdot \text{Ceq} \cdot \text{Vinmax}^2 = 7.762 \times 10^{-6} \text{J}$  $26\mu J > 7.7\mu J$ Second Condition Deadtime > Time required to charge/discharge the total cap Co\_tr is the time related capaitance when Vds is rising from 0 to 400V Crss eff can be taken as 1/2 or 1/3 of Crss Co\_tr := 182pF Crss\_eff := 2.5pF Cwell := 5pF CHB :=  $2Co_tr + Crss_eff + Cwell = 3.715 \times 10^{-10} F$

LLC resonant half-bridge converter operation

LLC resonant half-bridge converter operation

Tch = CHB

$$\frac{Vinmax}{L_noload} = 3.969 \times 10^{-7} s$$

Tdeadtime := Tch + t1 + 50ns = 4.756 × 10<sup>-7</sup> s

new\_Tdeadtime := Tdeadtime = 4.756 × 10<sup>-7</sup> s

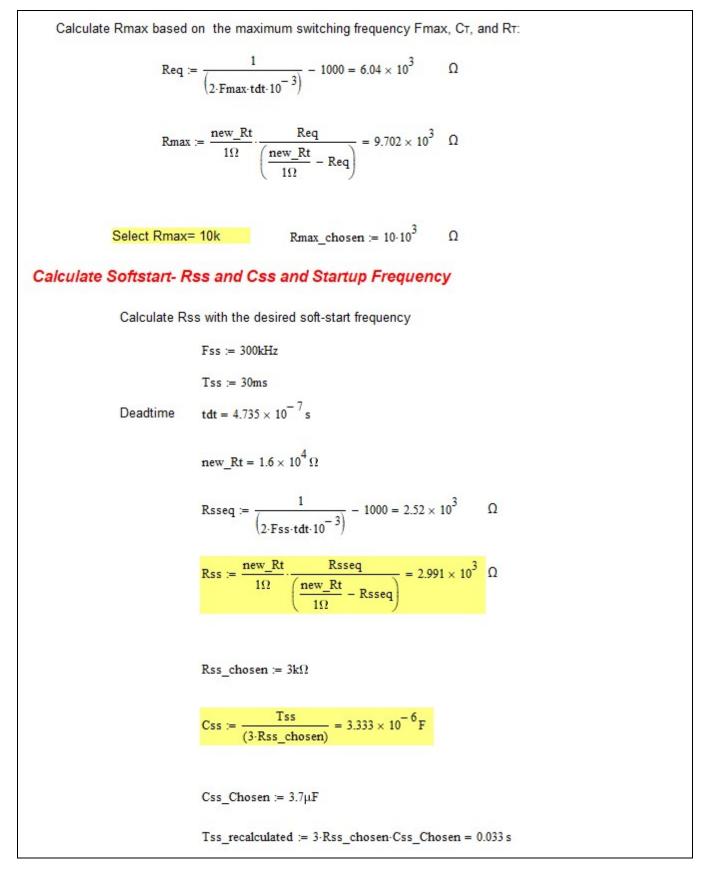

**Calculate RT and CT capacitor for IRS27952 Half bridge LLC IC**

$C_{t} := \frac{\left(\frac{\text{new}_T \text{deadtime}}{1s} \cdot 10^{-3} - 40 \cdot 10^{-12}\right)}{0.85} = 5.125 \times 10^{-10}$

Ct capacitor should be equal or bigger than the calculated value for ZVS operation:

$\text{new}_C t := 510 \text{pF}$  We chose 510 pF which is a standard value

Calculate the actual dead-time per the selected Cr value:

$tdt := (0.85 \cdot \text{new}_C \text{t} + 40 \text{pF}) \cdot 2 \frac{V}{2mA} = 4.735 \times 10^{-7} \text{ s}$

Fmin1 = 61.834 kHz

Calculate RT per the minimum switching frequency Fmin and Cr:

$\text{Rt} := \frac{1}{(2 \cdot \text{Fmin1} \cdot \text{tdt} \cdot 10^{-3})} - 1000 = 1.608 \times 10^4 \quad \Omega$

RT resistor should be smaller than the calculated value to keep ZVS operation

Select RT = 16k ext{ new Rt} = 16kt9

LLC resonant half-bridge converter operation

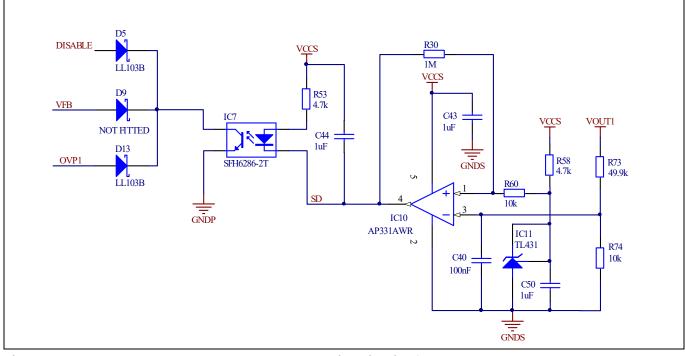

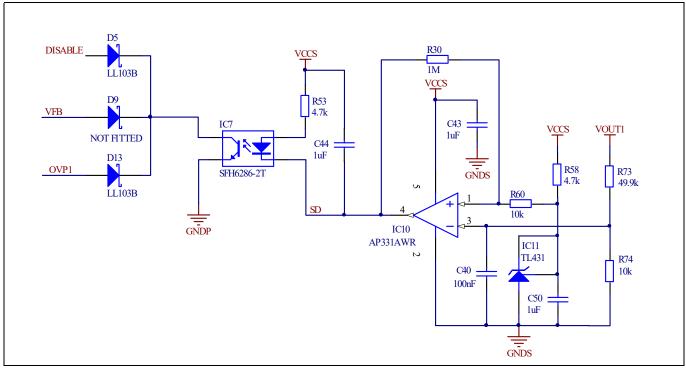

## 9.4 OVP circuit (hiccup mode operation)

The following circuit has been used to implement the light/open-load burst mode operation of the LLC resonant converter. Under light-load conditions the LLC resonant converter voltage feedback loop attempts to drive the switching frequency higher to prevent the output voltage rising above the target level. However, as frequency increases a point is reached at which ZVS operation is no longer possible. In a hard switching scenario the half-bridge MOSFETs would begin to suffer high switching losses leading to over-heating. To avoid this, the maximum permitted switching frequency is set below the ZVS region upper boundary. However, to prevent output voltage at light load from exceeding an acceptable level, it now becomes necessary to introduce hiccup mode over-voltage protection, which enables the converter to operate in short bursts..

The following circuit reduces system standby power by disabling the PFC section and the LLC section through an opto-isolator (IC7), which provides pull-down through three Schottky diodes connected to its collector. The open-collector output of IC10 transitions low when the converter output voltage rises above a defined level providing current to the diode of IC7. The comparator circuit includes a resistor (R30) to provide hysteresis so that when the output capacitors discharge sufficiently the circuit will deactivate. In this way burst mode operation is implemented with controllable on and off periods to maintain the correct output voltage at light load or in an open circuit.

Figure 24 OVP circuit for the IRS27952-based LLC resonant converter

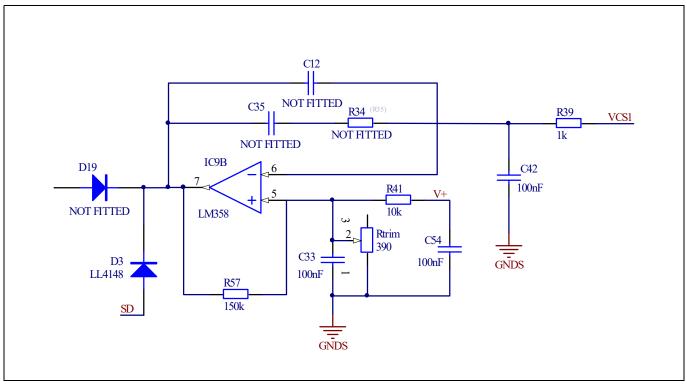

### 9.5 Over-current protection

Over-current protection is implemented with the following high output current detection circuit. IC9 and IC10 are supplied form the auxiliary power supply so that they are able to continue functioning when the output is shorted.

Figure 25 OCP circuit for the IRS27952-based LLC resonant converter

The circuit based around IC9B provides over-current protection sensed through the output current shunt resistors Rcs3, 4, 5, 6 and 8. The threshold is set by adjusting Rtrim, which is set to trigger protection in the 18 to 19 A range. When the output current exceeds this limit, the output of IC9B transitions low causing conduction through the diode of opto-isolator IC4 through D19 if D19 is installed. Since IC4 is used for both voltage and current feedback, D19 and D12 may be used to OR the outputs from IC9a (voltage feedback) and IC9b (over-current detection) so that either may cause the switching frequency to be increased to reduce output power as IC4 pulls down on the RT input of IC5 through Rmax. In this implementation the over-current protection circuit utilizes IC9B as a comparator with hysteresis provided by R57 and connected to IC7 through D3 providing ORing with the open-collector output of IC10<sup>1</sup>. Hiccup-mode protection is provided through D5, which is connected to the base of Q7. This causes C11 supplying VCC to IC5 to discharge to a voltage below the UVLO negative threshold<sup>2</sup>. IC5 then ceases to oscillate so that power transfer is interrupted. The PFC section is also disabled during this time through D13. The output current then falls and Q7 is released as the output of IC9B transitions positive again so that C11 is able to re-charge back up to the UVLO positive threshold of IC5. This cycle repeats until the overload condition is removed from the output.

<sup>&</sup>lt;sup>1</sup> This circuit has been modified from a current feedback loop controlling the switching frequency to a hiccup mode protection scheme. This is why C12, C35 and R34 have been removed and R57 has been added.

<sup>&</sup>lt;sup>2</sup> D9 has been removed from the circuit as it was found that small leakage currents through this diode can affect the operation of the oscillator of IC5.

### 9.6 Short-circuit protection

As mentioned earlier, the IRS27952 includes a high current shut-down function, which uses the on-state resistance of the low-side MOSFET sensed at the VS pin with a nominal threshold of 3 V that triggers a latched shut-down of the gate drive outputs.

However, it cannot be guaranteed that the primary tank circuit during an output short circuit will be high enough to trigger this protection mechanism. Furthermore, the tank current would need to reach a peak in the region of 10 A to trigger this protection. In this design the over-current protection scheme described in the previous section also provides short-circuit protection therefore the system would enter hiccup mode befre ever triggering protection previously described, which is considered to be a safer and more reliable approach.

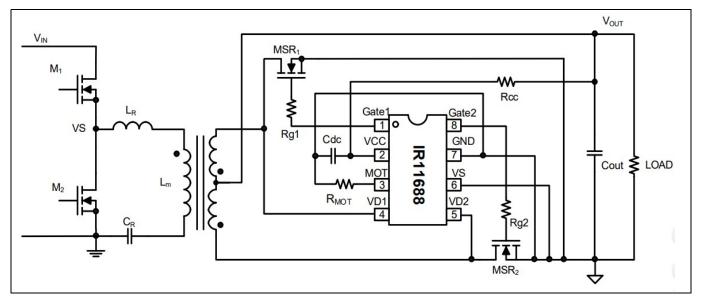

## 10 IRS11688 functional overview

The IRS11688 Synchronous Rectifier (SR) control IC drives a pair of N-channel power MOSFETs, forming the rectifying output stage of a resonant half-bridge converter. The drain-to-source voltage of each SR MOSFET is directly sensed to determine the level of conducted current so that the MOSFET can be turned on and off in close proximity to the zero current transition. Built-in shoot-through protection logic prevents both channels from ever being able to turn on at the same time. Internal blanking, reverse current protection and double pulse suppression enable reliable operation in all operating modes.

The IRS11688 precisely controls switching on and off of the synchronous MOSFETs, thereby bypassing their body diodes during the secondary conduction phases to emulate the rectifying action of a dual-diode rectifier while eliminating the majority of conduction losses. The MOSFET drain-to-source voltages are sensed at millivolt levels to determine the magnitude and polarity of the drain current so that the IRS11688 can switch the gates on and off appropriately. The high-voltage input structure allows the IRS11688 to withstand up to 200 V from direct connection to each drain pin. The IRS11688-based smart Synchronous Rectifier (SR) offers significant efficiency improvement in resonant converters over the full load range. Replacement of a Schottky diode output rectifier with the IRS11688, combined with a pair of correctly selected high-performance MOSFETs, provides significantly reduced power dissipation.

The IRS11688 is able to operate from wide  $V_{cc}$  supply voltage ranging from 4.75 V to 20 V, enabling it to be supplied from the output in a 5 V system without the need for an auxiliary transformer winding. A logic-level MOSFET is required for low output (low  $V_{cc}$ ) voltage applications. A built-in arming and triggering mechanism allows correct switching on and off of the SR MOSFET under all system conditions, offering improved system reliability over a basic self-driven SR scheme or earlier generations of SR controller.

In addition, the IRS11688 enters a power-saving mode if neither VD sensing input detects a transition for more than an internally defined waiting time (typically 500 μs). In this mode supply current reduces to a few hundreds of micro amps, reducing quiescent power consumption and improving system standby and light-load efficiency.

|              | Pin                    | Name                                | Description                     |

|--------------|------------------------|-------------------------------------|---------------------------------|

| Gate1Gate2   | 1                      | GATE1                               | Gate drive output 1             |

| 1 o 🗸 🔋      | 2                      | VCC                                 | Supply voltage                  |

| VCC _ GND    | 3                      | мот                                 | Minimum on-time program input   |

| 2 <b>ग</b> 7 | 4                      | VD1 SR MOSFET 1 drain voltage sense |                                 |

| мот 🗅 vs     | <b>1</b> VS <b>5</b> V |                                     | SR MOSFET 2 drain voltage sense |

| 3 <b>8</b> 6 | 6                      | VS                                  | SR MOSFET source voltage sense  |

| VD1 00 VD2 7 |                        | GND                                 | Analog and power ground         |

| 4 5          | 8                      | GATE2                               | Gate drive output 2             |

The IRS11688 is available in a SO-8 package. The pin-out is shown below:

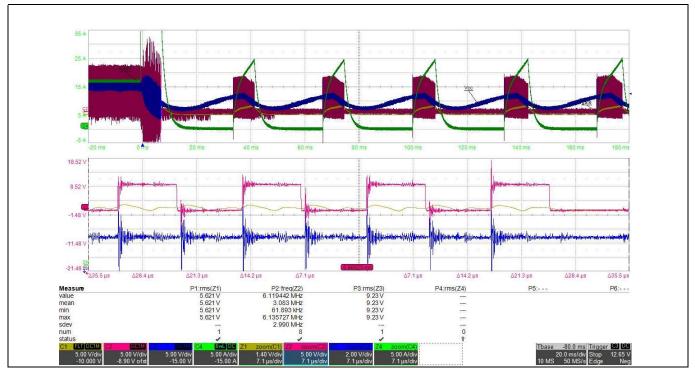

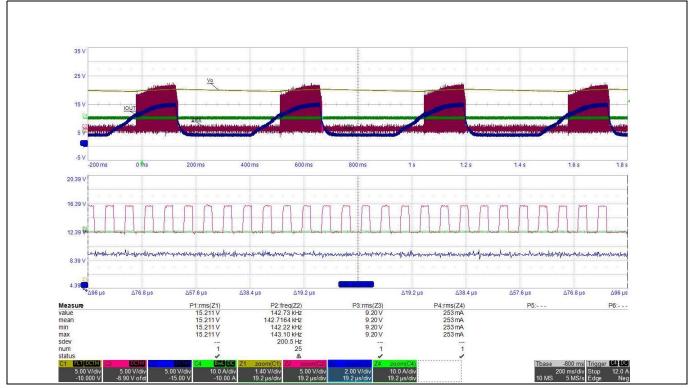

### Figure 26 IRS11688 pin assignments

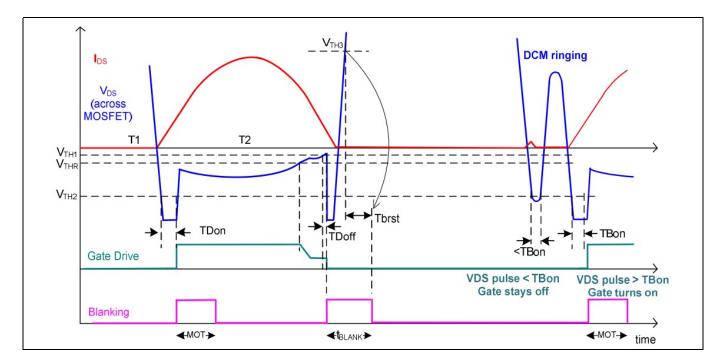

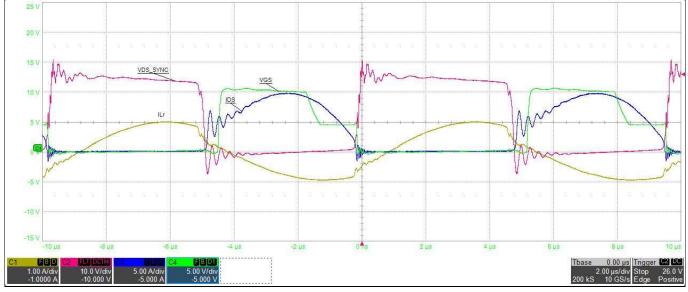

The operating waveforms shown in figure 28 show one side of the split secondary dual MOSFET SR. During period T1 there is no current in this branch of the secondary. The T2 phase begins when the corresponding primary switch is turned on and energy is transferred through the transformer to be delivered to the load through the output rectifier circuit. At this point the conduction phase of the branch SR MOSFET is initiated and current starts flowing through its body diode to produce a negative  $V_{DS}$  voltage. The body diode has a much higher voltage drop than the turn-on threshold  $V_{TH2}$ , causing the IR11688 to drive the gate of the SR MOSFET on to bypass it. When the MOSFET is turned on the instantaneous sensed voltage reduces to I·R<sub>DS(on)</sub>. This voltage

IRS11688 functional overview

level, being much lower than body diode forward voltage drop, is sensitive to parasitic ringing generated by the transformer leakage inductance and MOSFET output capacitance. To avoid false triggering and resulting premature gate turn-off, a blanking period (MOT) is set that disables V<sub>TH1</sub> triggering for a minimum period of time set by an external resistor. This avoids premature turn-off from occurring shortly after turn-on, by maintaining the MOSFET on for a minimum amount of time regardless of ringing transitions.

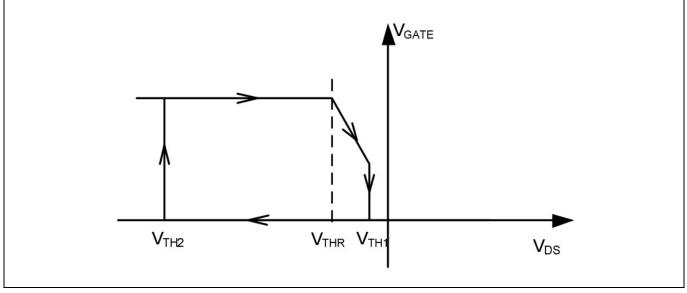

Once the SR MOSFET has been turned on, it remains on until the rectified current decays to a level where  $V_{DS}$  falls to the regulation threshold  $V_{THR}$ . At this point the gate drive pull-up is switched off and the gate drive output remains in a high impedance state with a weak pull-down to slowly discharge the gate voltage. The MOSFET channel resistance increases as gate voltage drops, moving toward the linear region of operation and thereby maintaining the negative  $V_{DS}$  voltage drop, more negative than the turn-off threshold  $V_{TH1}$ . The discharge circuit is maintained to keep  $V_{DS}$  voltage regulated around  $V_{THR}$  as current falls, thereby extending the MOSFET conduction period and enabling light-load operation.

Figure 27 Typical schematic of a resonant half-bridge converter with IR11688 SR controller

### Figure 28 Typical operating waveform of the IR11688

Eventually, as the MOSFET channel current reduces further toward zero, the  $V_{DS}$  voltage crosses threshold  $V_{TH1}$  and the IR11688 turns the gate off. The gate drive regulation function is illustrated in figure 29:

Figure 29 IR11688 voltage sensing thresholds

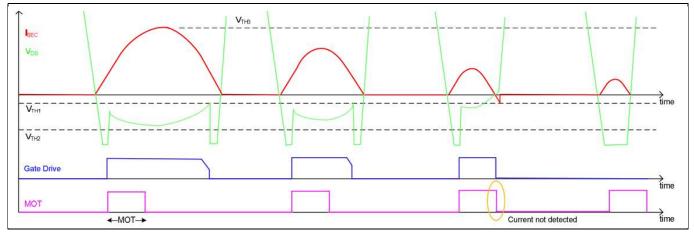

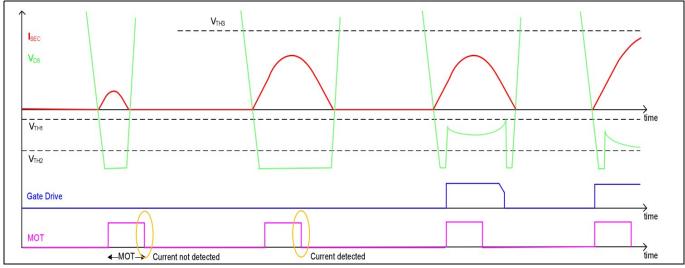

When the IR11688 turns the gate off, current again starts flowing through the body diode, which causes the  $V_{DS}$  voltage to make a sharp negative transition. Depending on the amount of residual current,  $V_{DS}$  may once again exceed the turn-on threshold  $V_{TH2}$ . For this reason re-triggering is disabled after the gate drive has been switched off until the controller has re-armed. The re-arming sequence requires  $V_{DS}$  to cross the positive  $V_{TH3}$  threshold and remain above it for a period denoted as  $t_{BRST}$ . If this does not occur the gate drive will remain low for a period of  $t_{BLANK}$ , after which time re-arming will occur automatically, to achieve high system efficiency combined with low standby loss. As mentioned, the IR11688 incorporates a programmable minimum on-time (MOT) to provide flexibility when using the IR11688 in various applications operating at different switching frequencies. The MOT function effectively sets the shut-down point at light load. During normal operation, the designer sets the minimum on-time to be shorter than the secondary conduction period. At progressively lighter loads, the conduction period reduces until it is eventually shorter than the MOT. If the IR11688 detects no voltage drop signifying no SR drain current, the MOT protection function causes the gate drive to be disabled for the next cycle. This MOT protection operates whether or not the SR gate drive is on, that is if conduction is through the drain-source channel or the body diode. In this way the IR11688 does not drive the gate at light loads and therefore consumes minimal power, improving system efficiency.

MOT protection as load decreases

Figure 31 Gate drive resuming as load increases

The IR11688 includes a turn-on leading-edge blanking function to prevent misfiring that could be triggered by high frequency ringing in DCM operation. In DCM the drain voltage of the SR MOSFET can resonate when secondary current transitions in each half-cycle. This V<sub>DS</sub> ringing, as shown in figure 28, could drop below zero volts under certain conditions, such as higher body diode voltage drop or longer body diode reverse recovery. To avoid false triggering by negative ringing, the IR11688 only triggers if V<sub>DS</sub> is lower than V<sub>TH2</sub> and longer than blanking time T<sub>bon</sub>. Therefore, in the case of a short spike or ringing the IR11688 will not switch on the MOSFET gate and the internal MOT timer will not be initiated, preventing a false trigger event and resulting shoot-through current. In a regular conduction cycle V<sub>DS</sub> remains lower than V<sub>TH2</sub> for more than T<sub>bon</sub>, and so the gate turns on after T<sub>bon</sub> expires. The total turn-on delay T<sub>don</sub> and the MOT time limit the minimum conduction time of the secondary rectifiers, and hence the maximum switching frequency of the converter with which it can effectively operate.

## **10.1** MOT resistor calculation

The MOT is linear in relation to the resistor value  $R_{MOT}$ . The following formula can be used to determine the required value:

$$R_{MOT} = 5.10^{10} \cdot t_{MOT}$$

The value of  $R_{MOT}$  should not be lower than the minimum recommended on the datasheet. On this board a standard value of 40.2 k $\Omega$  is used at the MOT pin of the IC. This value gives a minimum on-time of 800 ns.

[30]

ICE5QR0680AG functional overview

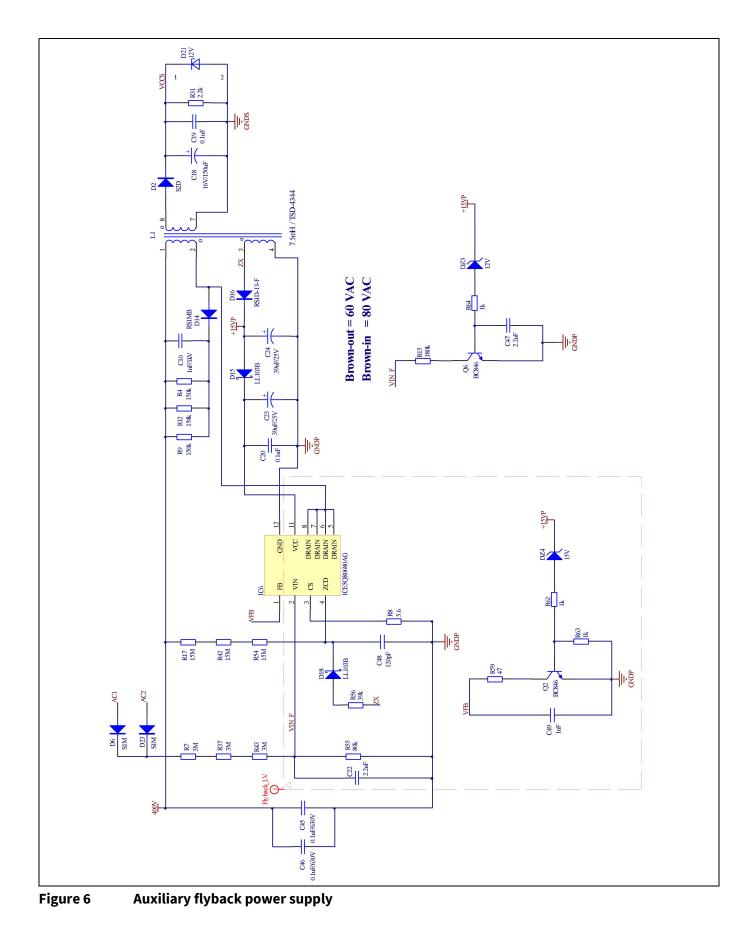

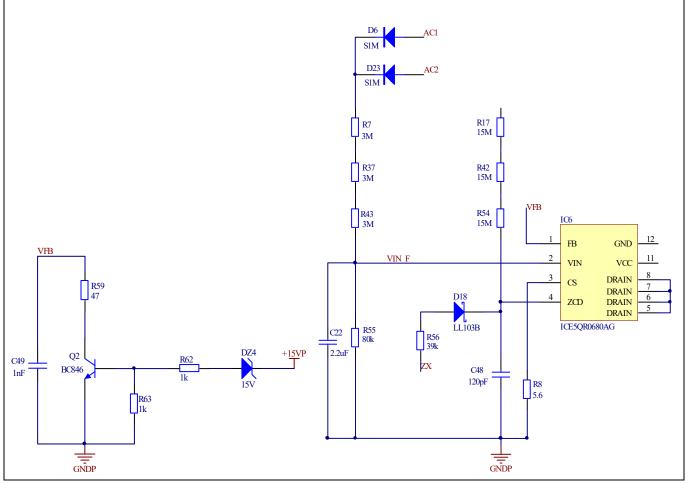

## **11** ICE5QR0680AG functional overview

For low output power applications, the flyback converter is the most widely used topology when galvanic isolation and/or multiple output are required, because it has a low system cost and is easy to design. It is used as an auxiliary "housekeeping" power supply for higher-power applications (e.g. air-conditioners, PC power, server power, industrial SMPS, etc.).

Figure 32 QR flyback converter

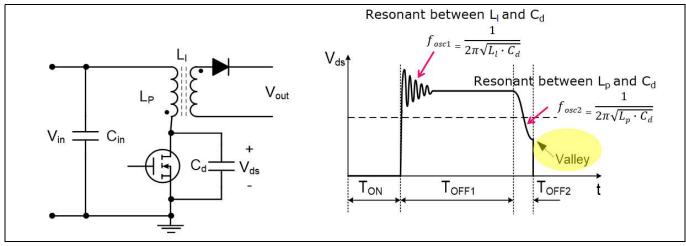

## 11.1 Quasi-Resonant (QR) flyback converter operation

When the primary MOSFET is turned on in the flyback converter the current through the primary side of the transformer begins to ramp up and energy is stored in the transformer core air gap. When the MOSFET turns off, the energy stored in the gap is transferred to the secondary side of the flyback converter. The flyback transformer leakage inductance ( $L_l$ ) also has some energy stored in it, which does not get transferred to the secondary. Instead this energy transfers to the combined drain-to-source capacitance seen at the MOSFET C<sub>d</sub>, which consists of the MOSFET C<sub>OSS</sub>, the transformer parasitic capacitance, trace capacitances and any other capacitance that may be present at the drain node. An LC ringing occurs with the period set by the C<sub>d</sub> resonating with the leakage inductance L<sub>l</sub>.